MORGAN & CLAYPOOL PUBLISHERS

# Embedded Systems Design with the Amtel AVR Microcontroller

Steven F. Barrett

Synthesis Lectures on Digital Circuits and Systems

Mitchell A. Thornton, Series Editor

Embedded Systems Design with the Atmel AVR Microcontroller Part I

# Synthesis Lectures on Digital Circuits and Systems

Editor Mitchell A. Thornton, *Southern Methodist University*

**Embedded Systems Design with the Atmel AVR Microcontroller – Part I** Steven F. Barrett 2009

**Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller II: Digital and Analog Hardware Interfacing** Douglas H. Summerville 2009

**Designing Asynchronous Circuits using NULL Convention Logic (NCL)** Scott C. Smith, JiaDi 2009

Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller I: Assembly Language Programming

Douglas H.Summerville 2009

**Developing Embedded Software using DaVinci & OMAP Technology** B.I. (Raj) Pawate 2009

**Mismatch and Noise in Modern IC Processes** Andrew Marshall 2009

Asynchronous Sequential Machine Design and Analysis: A Comprehensive Development of the Design and Analysis of Clock-Independent State Machines and Systems Richard F. Tinder 2009

**An Introduction to Logic Circuit Testing** Parag K. Lala 2008 **Pragmatic Power** William J. Eccles 2008

**Multiple Valued Logic: Concepts and Representations** D. Michael Miller, Mitchell A. Thornton 2007

**Finite State Machine Datapath Design, Optimization, and Implementation** Justin Davis, Robert Reese 2007

Atmel AVR Microcontroller Primer: Programming and Interfacing Steven F. Barrett, Daniel J. Pack 2007

**Pragmatic Logic** William J. Eccles 2007

**PSpice for Filters and Transmission Lines** Paul Tobin 2007

**PSpice for Digital Signal Processing** Paul Tobin 2007

**PSpice for Analog Communications Engineering** Paul Tobin 2007

**PSpice for Digital Communications Engineering** Paul Tobin 2007

**PSpice for Circuit Theory and Electronic Devices** Paul Tobin 2007

**Pragmatic Circuits: DC and Time Domain** William J. Eccles 2006

**Pragmatic Circuits: Frequency Domain** William J. Eccles 2006

iv

### **Pragmatic Circuits: Signals and Filters** William J. Eccles

2006

### High-Speed Digital System Design

Justin Davis 2006

### **Introduction to Logic Synthesis using Verilog HDL** Robert B.Reese, Mitchell A.Thornton 2006

### Microcontrollers Fundamentals for Engineers and Scientists Steven F. Barrett, Daniel J. Pack

v

2006

Copyright © 2010 by Morgan & Claypool

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopy, recording, or any other except for brief quotations in printed reviews, without the prior permission of the publisher.

Embedded Systems Design with the Atmel AVR Microcontroller - Part I

Steven F. Barrett

www.morganclaypool.com

ISBN: 9781608451272 paperback ISBN: 9781608451289 ebook

DOI 10.2200/S00138ED1V01Y200910DCS024

A Publication in the Morgan & Claypool Publishers series SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS

Lecture #24 Series ISSN Synthesis Lectures on Digital Circuits and Systems Print 1932-3166 Electronic 1932-3174

# Embedded Systems Design with the Atmel AVR Microcontroller Part I

Steven F. Barrett University of Wyoming

SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS #24

### ABSTRACT

This textbook provides practicing scientists and engineers an advanced treatment of the Atmel AVR microcontroller. This book is intended as a follow on to a previously published book, titled "Atmel AVR Microcontroller Primer: Programming and Interfacing." Some of the content from this earlier text is retained for completeness. This book will emphasize advanced programming and interfacing skills. We focus on system level design consisting of several interacting microcontroller subsystems. The first chapter discusses the system design process. Our approach is to provide the skills to quickly get up to speed to operate the internationally popular Atmel AVR microcontroller line by developing systems level design skills. We use the Atmel ATmega164 as a representative sample of the AVR line. The knowledge you gain on this microcontroller can be easily translated to every other microcontroller in the AVR line. In succeeding chapters, we cover the main subsystems aboard the microcontroller, providing a short theory section followed by a description of the related microcontroller subsystem with accompanying software for the subsystem. We then provide advanced examples exercising some of the features discussed. In all examples, we use the C programming language. The code provided can be readily adapted to the wide variety of compilers available for the Atmel AVR microcontroller line. We also include a chapter describing how to interface the microcontroller to a wide variety of input and output devices. The book concludes with several detailed system level design examples employing the Atmel AVR microcontroller.

### **KEYWORDS**

Atmel microcontroller, Atmel AVR, ATmega164, microcontroller interfacing, embedded systems design

# Contents

|   | Ackn   | cknowledgments xv                                           |  |  |

|---|--------|-------------------------------------------------------------|--|--|

|   | Prefac | cexvii                                                      |  |  |

| 1 | Embe   | edded Systems Design                                        |  |  |

|   | 1.1    | What is an embedded system?                                 |  |  |

|   | 1.2    | Embedded system design process1                             |  |  |

|   |        | 1.2.1 Problem Description 3                                 |  |  |

|   |        | 1.2.2 Background Research 3                                 |  |  |

|   |        | 1.2.3 Pre-Design 3                                          |  |  |

|   |        | 1.2.4 Design 5                                              |  |  |

|   |        | 1.2.5 Implement Prototype 6                                 |  |  |

|   |        | 1.2.6 Preliminary Testing 7                                 |  |  |

|   |        | 1.2.7 Complete and Accurate Documentation 7                 |  |  |

|   | 1.3    | Example: Kinesiology and Health Laboratory Instrumentation7 |  |  |

|   | 1.4    | Summary                                                     |  |  |

|   | 1.5    | Chapter Problems                                            |  |  |

|   | Refer  | ences                                                       |  |  |

| 2 | Atme   | AVR Architecture Overview                                   |  |  |

|   | 2.1    | ATmega164 Architecture Overview                             |  |  |

|   |        | 2.1.1 Reduced Instruction Set Computer—RISC 15              |  |  |

|   |        | 2.1.2 Assembly Language Instruction Set 16                  |  |  |

|   |        | 2.1.3 C Operator Size 17                                    |  |  |

|   |        | 2.1.4 Bit Twiddling 17                                      |  |  |

|   |        | 2.1.5 ATmega164 Architecture Overview 18                    |  |  |

ix I

### x CONTENTS

| 2.2   | Nonvolatile and Data Memories                      |  |

|-------|----------------------------------------------------|--|

|       | 2.2.1 In-System Programmable Flash EEPROM 19       |  |

|       | 2.2.2 Byte-Addressable EEPROM 20                   |  |

|       | 2.2.3 Accessing Byte-Addressable EEPROM Example 20 |  |

|       | 2.2.4 Static Random Access Memory (SRAM) 21        |  |

|       | 2.2.5 Programmable Lock Bits 21                    |  |

| 2.3   | Port System                                        |  |

| 2.4   | Peripheral Features—Internal Subsystems            |  |

|       | 2.4.1 Time Base 24                                 |  |

|       | 2.4.2 Timing Subsystem 24                          |  |

|       | 2.4.3 Pulse Width Modulation Channels 25           |  |

|       | 2.4.4 Serial Communications 25                     |  |

|       | 2.4.5 Analog to Digital Converter—ADC 26           |  |

|       | 2.4.6 Analog Comparator 26                         |  |

|       | 2.4.7 Interrupts 26                                |  |

| 2.5   | Physical and Operating Parameters                  |  |

|       | 2.5.1 Packaging 28                                 |  |

|       | 2.5.2 Power Consumption 28                         |  |

|       | 2.5.3 Speed Grades 28                              |  |

| 2.6   | Choosing a Microcontroller                         |  |

| 2.7   | Application: ATmega164 Testbench                   |  |

|       | 2.7.1 Hardware Configuration 30                    |  |

|       | 2.7.2 Software Configuration 32                    |  |

| 2.8   | Programming the ATmega164                          |  |

|       | 2.8.1 Programming Procedure 36                     |  |

| 2.9   | In-System Programming (ISP)                        |  |

| 2.10  | Software Portability                               |  |

| 2.11  | Summary                                            |  |

| 2.12  | Chapter Problems                                   |  |

| Refer | ences                                              |  |

|       |                                                    |  |

| CON | JTENTS | xi |

|-----|--------|----|

| COL |        | л  |

| 3 | Serial | Communication Subsystem                                   |

|---|--------|-----------------------------------------------------------|

|   | 3.1    | Serial Communications                                     |

|   |        | 3.1.1 ASCII 44                                            |

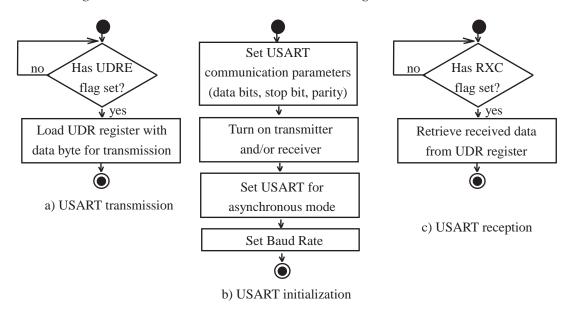

|   | 3.2    | Serial USART                                              |

|   |        | 3.2.1 System Overview 45                                  |

|   |        | 3.2.2 System Operation and Programming 48                 |

|   |        | 3.2.3 Full Duplex USART-based Microcontroller Link 51     |

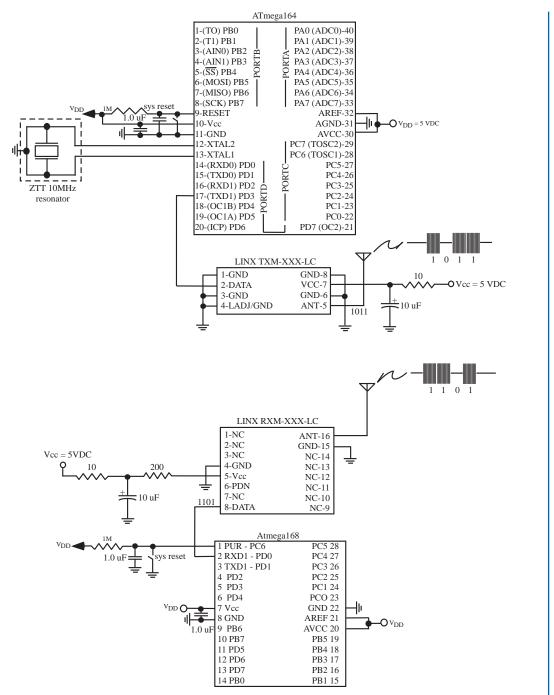

|   |        | 3.2.4 USART-based Radio Frequency Microcontroller Link 58 |

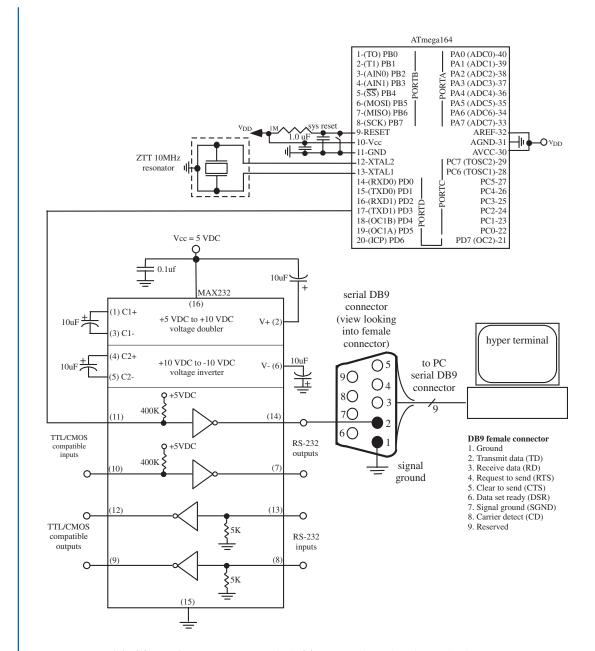

|   |        | 3.2.5 USART-to-PC 58                                      |

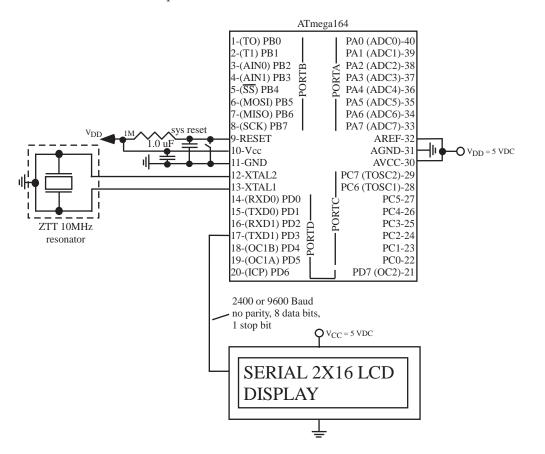

|   |        | 3.2.6 USART Serial Liquid Crystal Display 58              |

|   |        | 3.2.7 Serial Peripheral Interface—SPI 61                  |

|   |        | 3.2.8 Extending the Atmel AVR features via the SPI 65     |

|   | 3.3    | Networked Microcontrollers                                |

|   |        | 3.3.1 Two-wire Serial Interface 67                        |

|   |        | 3.3.2 Controller Area Network (CAN) 69                    |

|   |        | 3.3.3 Zigbee Wireless IEEE 802.15.4 Interface 69          |

|   | 3.4    | Summary                                                   |

|   | 3.5    | Chapter Problems                                          |

|   | Refer  | ences                                                     |

| 4 | Analo  | og to Digital Conversion (ADC)                            |

|   | 4.1    | Sampling, Quantization and Encoding                       |

|   |        | 4.1.1 Resolution and Data Rate 74                         |

|   | 4.2    | Analog-to-Digital Conversion (ADC) Process                |

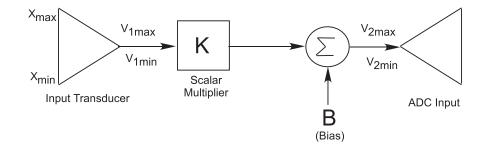

|   |        | 4.2.1 Transducer Interface Design (TID) Circuit 76        |

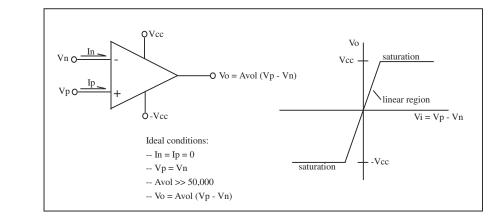

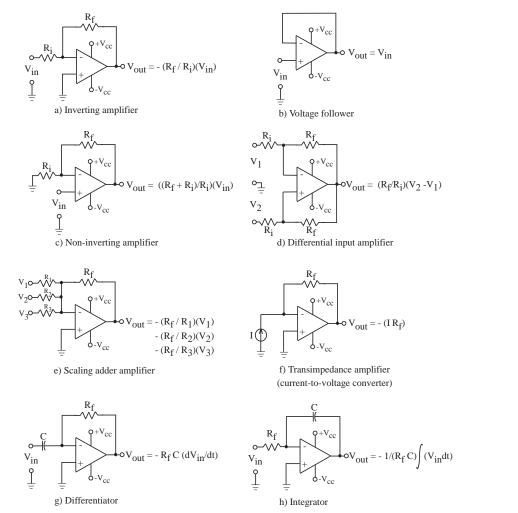

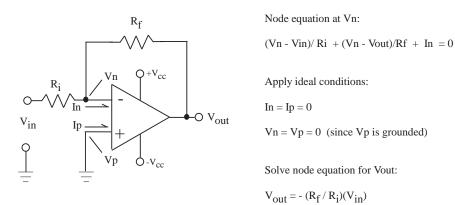

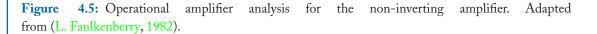

|   |        | 4.2.2 Operational Amplifiers 77                           |

|   | 4.3    | ADC Conversion Technologies                               |

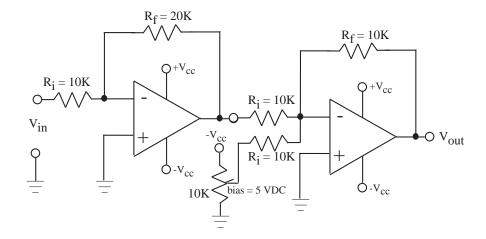

|   |        | 4.3.1 Successive-Approximation 81                         |

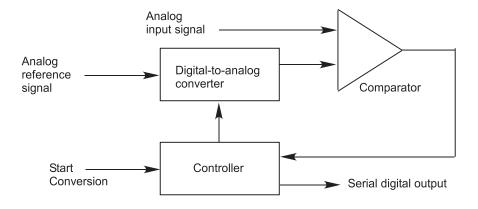

|   | 4.4    | The Atmel ATmega164 ADC System                            |

|   |        | 4.4.1 Block Diagram 83                                    |

### xii CONTENTS

|   |       | 4.4.2 Registers 83                                    |

|---|-------|-------------------------------------------------------|

|   |       | 4.4.3 Programming the ADC 86                          |

|   | 4.5   | Examples                                              |

|   |       | 4.5.1 ADC Rain Gage Indicator 87                      |

|   |       | 4.5.2 ADC Rain Gage Indicator with SPI 94             |

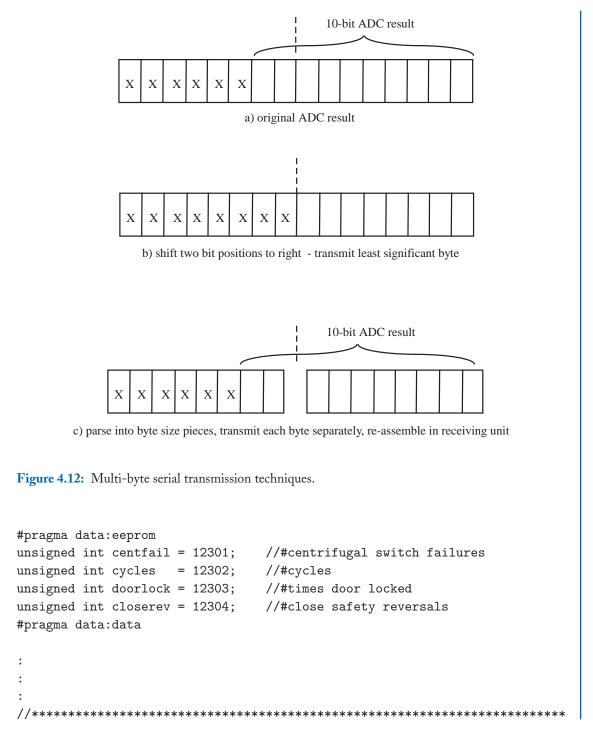

|   |       | 4.5.3 Transmitting ADC values via the USART or SPI 96 |

|   |       | 4.5.4 One-bit ADC - Threshold Detector 100            |

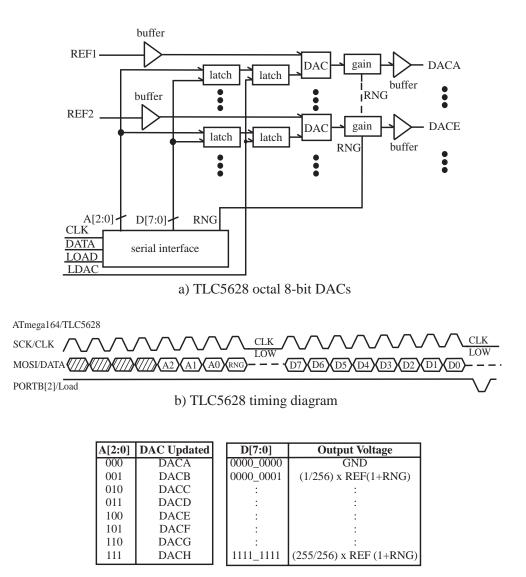

|   | 4.6   | Digital-to-Analog Conversion (DAC)100                 |

|   |       | 4.6.1 Octal Channel, 8-bit DAC via the SPI 102        |

|   | 4.7   | Summary                                               |

|   | 4.8   | Chapter Problems                                      |

|   | Refe  | rences                                                |

| 5 | Inter | rupt Subsystem                                        |

|   | 5.1   | Interrupt Theory                                      |

|   | 5.2   | ATmega164 Interrupt System                            |

|   | 5.3   | Programming an Interrupt System                       |

|   | 5.4   | Application                                           |

|   |       | 5.4.1 External Interrupts 110                         |

|   |       | 5.4.2 Internal Interrupt 112                          |

|   | 5.5   | Foreground and Background Processing115               |

|   | 5.6   | Interrupt Examples                                    |

|   |       | 5.6.1 Real Time Clock 116                             |

|   |       | 5.6.2 Interrupt Driven USART 119                      |

|   | 5.7   | Summary                                               |

|   | 5.8   | Chapter Problems                                      |

|   | Refe  | rences                                                |

| A | ATm   | nega164 Register Set                                  |

| В | ATm   | nega164 Header File                                   |

### CONTENTS xiii

| Author's Biography | · · · · · · · · · · · · · · · · · · · | •••••• |  |

|--------------------|---------------------------------------|--------|--|

| Index              |                                       |        |  |

# Acknowledgments

I would like to dedicate this book to my close friend and writing partner Dr. Daniel Pack, Ph.D., P.E. Daniel elected to "sit this one out" because of a thriving research program in unmanned aerial vehicles (UAVs). Daniel took a very active role in editing the final manuscript of this text. Also, much of the writing is his from earlier Morgan & Claypool projects. In 2000, Daniel suggested that we might write a book together on microcontrollers. I had always wanted to write a book but I thought that's what other people did. With Daniel's encouragement we wrote that first book (and five more since then). Daniel is a good father, good son, good husband, brilliant engineer, a work ethic second to none, and a good friend. To you, good friend, I dedicate this book. I know that we will do many more together.

Steven F. Barrett October 2009

## Preface

In 2006 Morgan & Claypool Publishers (M&C) released the textbook, titled "Microcontrollers Fundamentals for Engineers and Scientists." The purpose of the textbook was to provide practicing scientists and engineers with a tutorial on the fundamental concepts and the use of microcontrollers. The textbook presented the fundamental concepts common to all microcontrollers. This book was followed in 2008 with "Atmel AVR Microcontroller Primer: Programming and Interfacing." The goal for writing this follow-on book was to provide details on a specific microcontroller family – the Atmel AVR Microcontroller. This book is the third in the series. In it the emphasis is on system level design and advanced microcontroller interfacing and programming concepts. Detailed examples are provided throughout the text.

### **APPROACH OF THE BOOK**

We assume the reader is already familiar with the Atmel AVR microcontroller line. If this is not the case, we highly recommend a first read of "Atmel AVR Microcontroller Primer: Programming and Interfacing." Although some of the content from this earlier volume is retained in this current book for completeness, the reader will be much better served with a prior solid background in the Atmel AVR microcontroller family.

Chapter 1 contains an overview of embedded systems level design. Chapter 2 presents a brief review of the Atmel AVR subsystem capabilities and features. Chapters 3 through 7 provide the reader with a detailed treatment of the subsystems aboard the AVR microcontroller. Chapter 8 ties together the entire book with several examples of system level design.

Steven F. Barrett October 2009

### CHAPTER 1

# **Embedded Systems Design**

Objectives: After reading this chapter, the reader should be able to

- Define an embedded system.

- List all aspects related to the design of an embedded system.

- Provide a step-by-step approach to embedded system design.

- Discuss design tools and practices related to embedded systems design.

- Apply embedded system design practices in the design of a microcontroller system employing several interacting subsystems.

In this first, chapter we begin with a definition of just what is an embedded system. We then explore the process of how to successfully (and with low stress) develop an embedded system prototype that meets established requirements. We conclude the chapter with an extended example. The example illustrates the embedded system design process in the development and prototype of instrumentation for a kinesiology laboratory. We will revisit this example throughout the book.

### **1.1 WHAT IS AN EMBEDDED SYSTEM?**

An embedded system contains a microcontroller to accomplish its job of processing system inputs and generating system outputs. The link between system inputs and outputs is provided by a coded algorithm stored within the processor's resident memory. What makes embedded systems design so interesting and challenging is the design must also take into account the proper electrical interface for the input and output devices, limited on-chip resources, human interface concepts, the operating environment of the system, cost analysis, related standards, and manufacturing aspects (Anderson, 2008).

### **1.2 EMBEDDED SYSTEM DESIGN PROCESS**

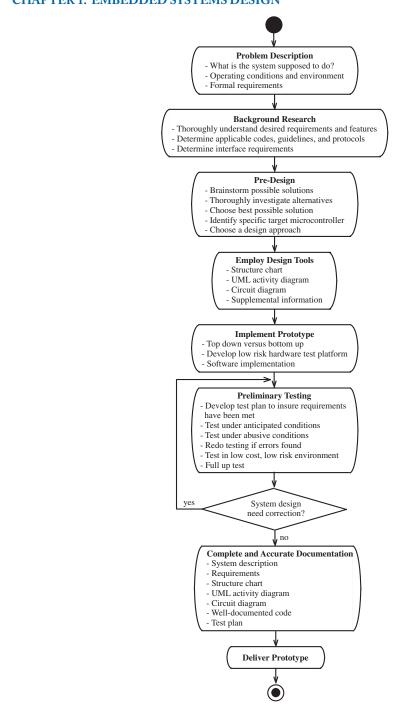

In this section, we provide a step-by-step approach to develop the first prototype of an embedded system that will meet established requirements. There are many formal design processes that we could study. We will concentrate on the steps that are common to most. We purposefully avoid formal terminology of a specific approach and instead concentrate on the activities that are accomplished as a system prototype is developed. The design process we describe is illustrated in Figure 1.1 using a Unified Modeling Language (UML) activity diagram. We discuss the proper construction process of activity diagrams later in the chapter.

Figure 1.1: Embedded system design process.

### 1.2. EMBEDDED SYSTEM DESIGN PROCESS 3

### **1.2.1 PROBLEM DESCRIPTION**

The purpose of the problem description step is to determine the goal of the system. To achieve this step, you must thoroughly investigate what the system is supposed to do. Questions to raise and answer during this step include but are not limited to:

- What is the system supposed to do?

- Where will it be operating and under what conditions?

- Are there any restrictions placed on the system design?

To answer these questions, the embedded designer interacts with the client to ensure clear agreement on what is to be done. The final result of this step is a detailed listing of system requirements and related specifications. The establishment of clear, definable requirements may necessitate considerable interaction between the design engineer and the client. It is essential that both parties agree on system requirements before proceeding further in the design process.

### **1.2.2 BACKGROUND RESEARCH**

Once a detailed list of requirements has been established, the next step is to perform background research related to the design. In this step, the designer will ensure they understand all requirements and features desired by the client. This will again involve interaction between the designer and the client. The designer will also investigate applicable codes, guidelines, protocols, and standards related to the project. This is also a good time to start thinking about the interface between different portions of the project, particularly, the input and output devices peripherally connected to the microcontroller. The ultimate objective of this step is to have a thorough understanding of the project requirements and related project aspects.

### 1.2.3 PRE-DESIGN

The goal of the pre-design step is to convert a thorough understanding of the project into possible design alternatives. Brainstorming is an effective tool in this step. Here, a list of alternatives is developed. Since an embedded system typically involves both hardware and/or software, the designer can investigate whether requirements could be met with a hardware only solution or some combination of hardware and software. Generally speaking, a hardware only solution executes faster; however, the design is fixed once fielded. On the other hand, software provides flexibility and a slower execution speed. Most embedded design solutions will use a combination of both to capitalize on the inherent advantages of each.

In this step, the designer must also investigate potential digital design technology solutions. There are a wide variety of alternatives including:

- programmable gate arrays,

- · microprocessors,

- digital signal processors (DSP),

- microcontrollers, and

- mixed mode processing combining available technologies.

A description of available technologies and their inherent features is provided in "Microcontrollers Fundamentals for Engineers and Scientists (Barrett, 2006)."

Once alternative design solutions have been investigated, it is now time to choose a single approach to develop into a full design. To make the final choice, the tradeoffs between competing designs must be evaluated. It is important to involve the client in this step.

Once a design alternative has been selected, the general partition between hardware and software can be determined. It is also an appropriate time to select a specific hardware device to implement the prototype design. If a microcontroller technology has been chosen, it is now time to select a specific controller. This is accomplished by answering the following questions:

- What microcontroller subsystems or features i.e., ADC, PWM, timer, etc.) are required by the design?

- How many input and output pins are required by the design?

- What is the expected maximum operating speed of the microcontroller expected to be?

- Is the specific microcontroller and a full complement of related documentation and support tools readily available? Employing the latest, new processor without complete documentation, support, and development tools leads to stress and frustration.

- As the design progresses, is it easy to migrate to a pin-for-pin compatible microcontroller with larger memory resources? Atmel makes this easy to do. For example, the ATmega164 (16K) is also available in a 32K variant (ATmega324) and a 64K variant (Atmega644).

- Is the specific microcontroller going to be available in sufficient quantities for a production run? You do not want to choose a specific controller that is too old or too new unless sufficient production quantities have been verified as being available.

- Are all required peripheral hardware readily available with a full complement of supporting documentation? Again, employing hardware without proper documentation leads to stress and frustration.

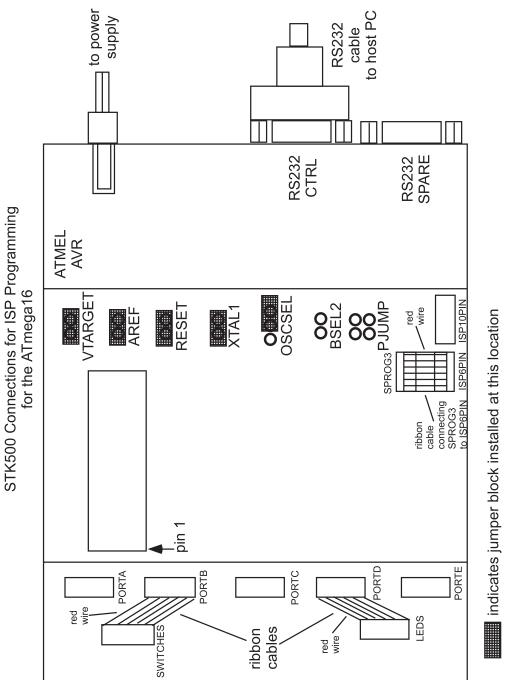

Choosing a specific microcontroller may seem a bit overwhelming. Atmel eases the stress by providing a complete family of microcontrollers. Also, Atmel's STK500 programming board (to be discussed in the next chapter) provides low cost programming support for virtually all controllers in the ATmega product line. For example, if the ATmega164 was chosen as the potential design solution, it is easy to migrate to a pin-for-pin compatible microcontroller with additional memory resources (ATmega324, ATmega644).

### 1.2. EMBEDDED SYSTEM DESIGN PROCESS 5

### 1.2.4 DESIGN

With a clear view of system requirements and features, a general partition determined between hardware and software, and a specific microcontroller chosen, it is now time to tackle the actual design. It is important to follow a systematic and disciplined approach to design. This will allow for low stress development of a documented design solution that meets requirements. In the design step, several tools are employed to ease the design process. They include the following:

- Employing a top-down design, bottom up implementation approach,

- Using a structure chart to assist in partitioning the system,

- · Using a Unified Modeling Language (UML) activity diagram to work out program flow, and

- Developing a detailed circuit diagram of the entire system.

Let's take a closer look at each of these. The information provided here is an abbreviated version of the one provided in "Microcontrollers Fundamentals for Engineers and Scientists." The interested reader is referred there for additional details and an indepth example (Barrett, 2006).

**Top down design, bottom up implementation.** An effective tool to start partitioning the design is based on the techniques of top-down design, bottom-up implementation. In this approach, you start with the overall system and begin to partition it into subsystems. At this point of the design, you are not concerned with how the design will be accomplished but how the different pieces of the project will fit together. A handy tool to use at this design stage is the structure chart. The structure chart shows the hierarchy of how system hardware and software components will interact and interface with one another. You should continue partitioning system activity until each subsystem in the structure chart has a single definable function (Page-Jones, 1988). A sample structure chart is provided in Section 1.3.

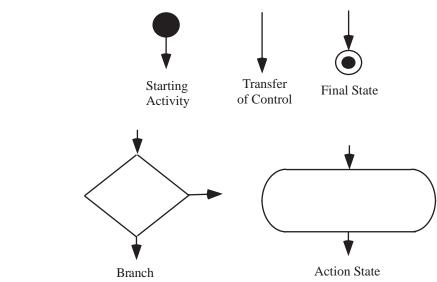

UML Activity Diagram. Once the system has been partitioned into pieces, the next step in the design process is to start working out the details of the operation of each subsystem we previously identified. Rather than beginning to code each subsystem as a function, we will work out the information and control flow of each subsystem using another design tool: the Unified Modeling Language (UML) activity diagram. The activity diagram is simply a UML compliant flow chart. UML is a standardized method of documenting systems. The activity diagram is one of the many tools available from UML to document system design and operation. The basic symbols used in a UML activity diagram for a microcontroller based system are provided in Figure 1.2 (Fowler, 2000).

To develop the UML activity diagram for the system, we can use a top-down, bottom-up, or a hybrid approach. In the top-down approach we begin by modeling the overall flow of the algorithm from a high level. If we choose to use the bottom-up approach, we would begin at the bottom of the structure chart and choose a subsystem for flow modeling. The specific course of action chosen depends on project specifics. Often, a combination of both techniques, a hybrid approach, is used. You should work out all algorithm details at the UML activity diagram level prior to coding any software. If you, first, can not explain the system operation at this higher level first, you have no

Figure 1.2: UML activity diagram symbols. Adapted from (Fowler, 2000).

business being in the detail of developing the code. Therefore, the UML activity diagram should be of sufficient detail so you can code the algorithm directly from it (Page-Jones, 1988).

In the design step, a detailed circuit diagram of the entire system is developed. It will serve as a roadmap to implement the system. It is also a good idea, at this point, to investigate available design information relative to the project. This would include hardware design examples, software code examples, and application notes available from manufacturers.

At the completion of this step, the prototype design is ready for implementation and testing.

### **1.2.5 IMPLEMENT PROTOTYPE**

To successfully implement a prototype, an incremental approach should be followed. Again, the top-down design, bottom-up implementation provides a solid guide for system implementation. In an embedded system design involving both hardware and software, the hardware system including the microcontroller should be assembled first, so the required signals of the software can interact. As the hardware prototype is assembled on a prototype board, each component is tested for proper operation as it is brought online. This allows the designer to pinpoint malfunctions as they occur. A low cost, low risk hardware prototype approach is discussed in more detail in the next chapter.

Once the hardware prototype is assembled, coding may commence. As before, software should be brought online incrementally. You may use a top down, bottom up, or hybrid approach, depending on the nature of the software. Because of bringing the software online in slow, stated increments, issues can be identified and corrected early on.

### 1.3. EXAMPLE: KINESIOLOGY AND HEALTH LABORATORY INSTRUMENTATION 7

### **1.2.6 PRELIMINARY TESTING**

To test the system, a detailed test plan must be developed. Tests should be developed to verify that the system meets all of its requirements and also intended system performance in an operational environment. The test plan should also include scenarios in which the system is used in an unintended manner. As before, a top-down, bottom-up, or hybrid approach can be used to test the system.

Once the test plan is completed, actual testing may commence. The results of each test should be carefully documented. As you go through the test plan, you will probably uncover a number of run time errors in your algorithm. After you correct a run time error, the entire test plan must be performed again. This ensures that the new fix does not have an unintended affect on another part of the system. Also, as you process through the test plan, you will probably think of other tests that were not included in the original test document. These tests should be added to the test plan. As you go through testing, realize your final system is only as good as the test plan that supports it!

Once testing is completed, you might try another level of testing where you intentionally try to "jam up" the system. In another words, try to get your system to fail by trying combinations of inputs that were not part of the original design. A robust system should continue to operate correctly in this type of an abusive environment. It is imperative that you design robustness into your system. When testing on a low cost simulator is complete, the entire test plan should be performed again with the actual system hardware. Once this is completed, you should have a system that meets its requirements!

### 1.2.7 COMPLETE AND ACCURATE DOCUMENTATION

With testing complete, the system design should be thoroughly documented. Much of the documentation will have already been accomplished during system development. Documentation will include the system description, system requirements, the structure chart, the UML activity diagrams documenting program flow, the test plan, results of the test plan, system schematics, and properly documented code. To properly document code, you should carefully comment all functions, describing their operation, inputs, and outputs. Also, comments should be included within the body of the function, describing key portions of the code. Enough detail should be provided such that code operation is obvious. It is also extremely helpful to provide variables and functions within your code names that describe their intended use.

You might think that a comprehensive system documentation is not worth the time or effort to complete it. Complete documentation pays rich dividends when it is time to modify, repair, or update an existing system. Also, well-documented code may often be reused in other projects: a method for efficient and timely development of new systems.

### 1.3 EXAMPLE: KINESIOLOGY AND HEALTH LABORATORY INSTRUMENTATION

To illustrate the design process, we provide an in depth example. The Kinesiology and Health (KNH) Department required assistance in developing a piece of laboratory research equipment. Members

of the research team met with the design engineer to describe the system and determine specific requirements.

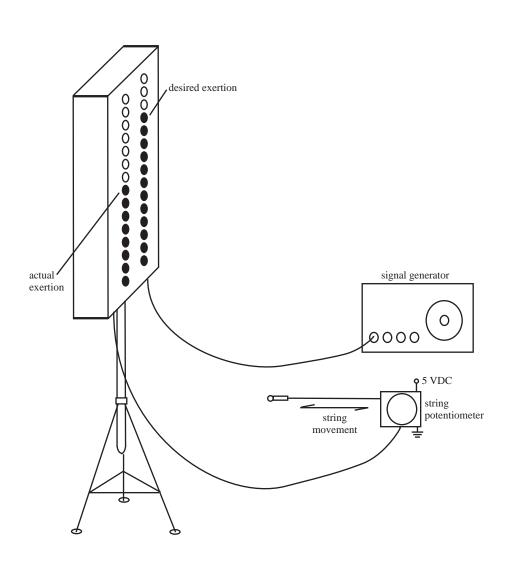

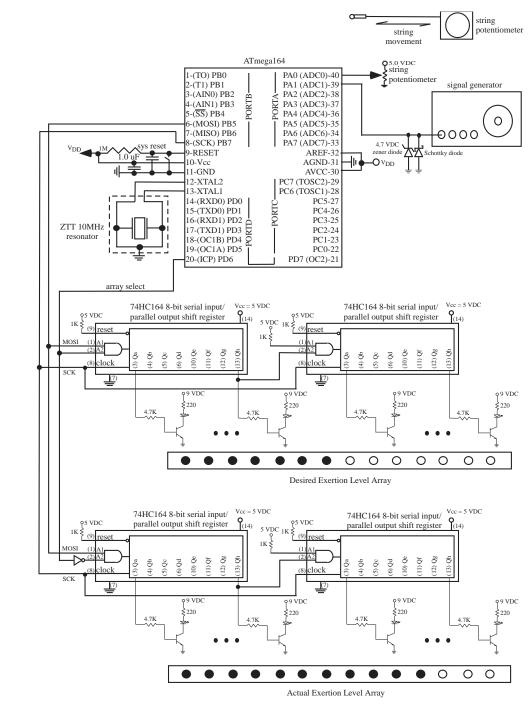

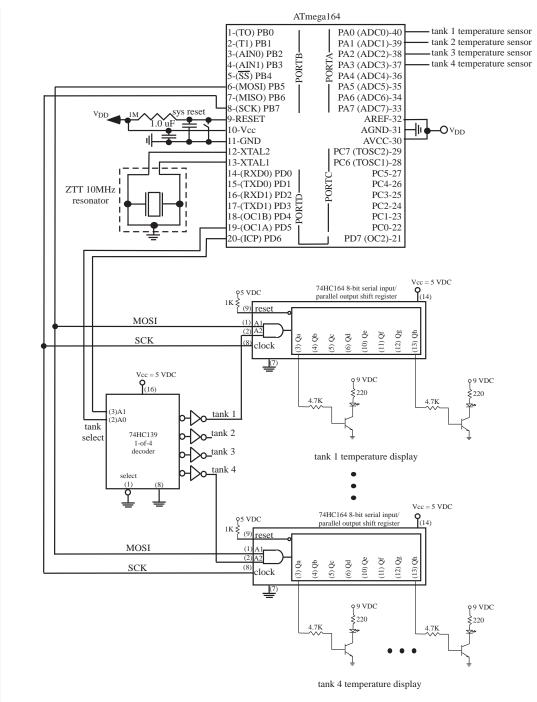

**Problem description and background research.** The system concept is illustrated in Figure 1.3. The KNH researchers needed a display panel containing two columns of large (10 mm diameter) red LEDs. The LEDs needed to be viewable at a distance of approximately 5 meters. The right column of LEDs would indicate the desired level of exertion for the subject under test. This LED array would be driven by an external signal generator using a low frequency ramp signal. The left column of LEDs would indicate actual subject exertion level. This array would be driven by a powered string potentiometer. As its name implies, a string potentiometer is equipped with a string pull. The resistance provided by the potentiometer is linearly related to the string displacement. Once powered, the string pot provides an output voltage proportional to the string pull length. The end of the string would be connected to a displacing arm on a piece of exercise equipment (e.g., a leg lift apparatus). After the requirements were determined, the characteristics of the available signal generator and the string pot were reviewed in detail.

**Pre-design.** With requirements clearly understood, the next step was to brainstorm possible solutions. Two possible alternatives clearly became evident: a complete hardware implementation or a microcontroller-based solution. Whichever approach was chosen, it was clear that the following features were required:

- The ability to independently drive a total of 28 large (10 mm diameter) LEDs.

- An interface circuit to drive each LED.

- Two analog-to-digital channels to convert the respective string potentiometer and signal generator inputs into digital signals.

- Input buffering circuitry to isolate and protect the panel from the string pot and signal generator and to guard against accidental setting overload.

- An algorithm to link the analog input signals to the appropriate LED activation signals.

A complete hardware implementation was chosen for the project. Due to the high number of output pins required to drive the LEDs and the minimal algorithm required to link the analog input to the LED outputs, it was determined that a microcontroller was not the best choice for this project. (Do not despair; we will implement this project using a microcontroller later in the book!)

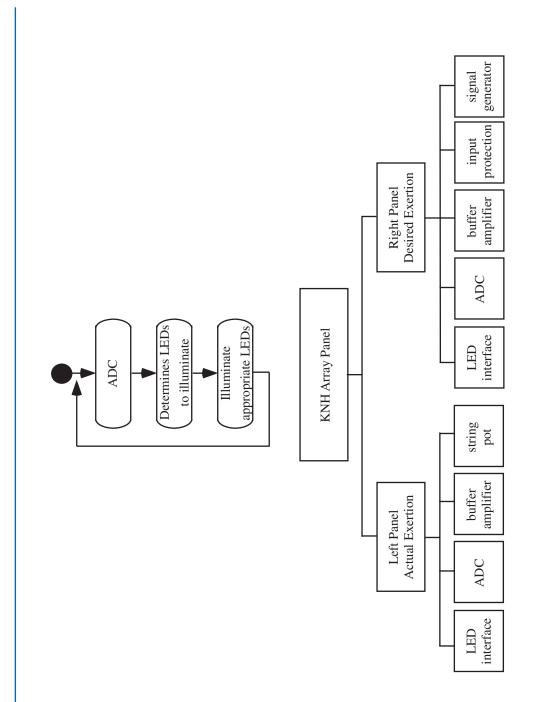

**Design.** With a design alternative chosen, the next step was to develop a detailed design. The overall project was partitioned using the structure chart illustrated in Figure 1.4.

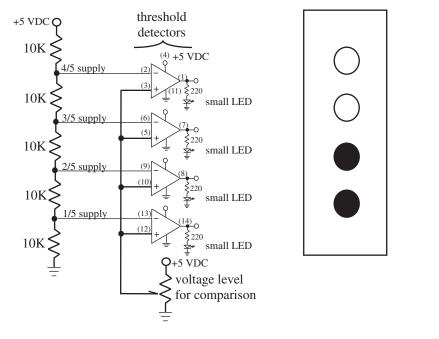

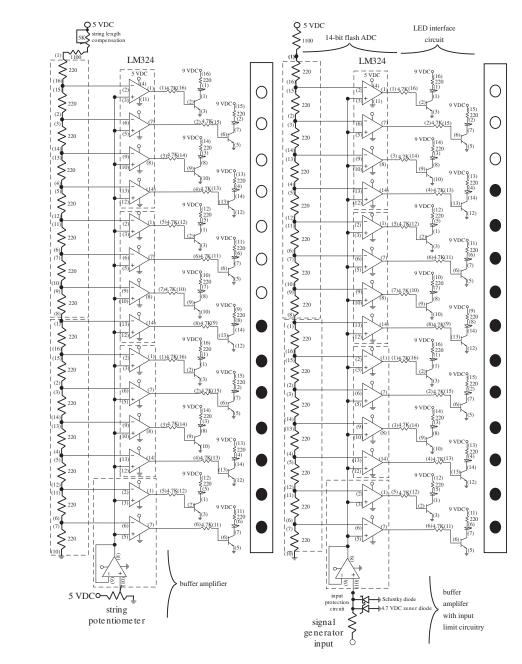

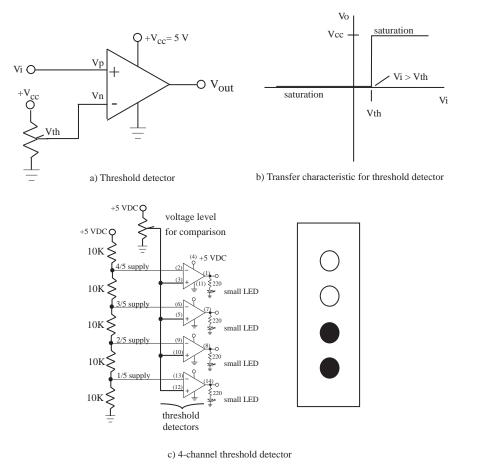

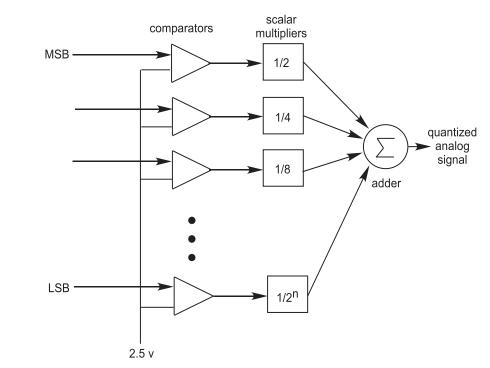

From the structure chart, a circuit diagram was developed for each subsystem within the circuit. To develop the analog-to-digital converter with a 14-bit output, a small test circuit using only 4 bits was first developed to test the concept. The small scale test circuit is shown in Figure 1.5. The full up, two array, 14-bit output driving a total of 28 large LEDs circuit diagram is provided in Figure 1.6. The LED circuit is described in greater detail in Chapter 7.

### 1.3. EXAMPLE: KINESIOLOGY AND HEALTH LABORATORY INSTRUMENTATION 9

**Figure 1.3:** KNH project overview. A display panel contains two arrays of 14 large (10 mm diameter) red LEDs each. The right array driven by a signal generator indicates the desired assertion level. The left array is driven by a string potentiometer transducer. This LED array indicates the actual exertion level as determined by the string length of the potentiometer.

# Figure 1.4: UML activity diagram and structure chart for KNH arrays.

### 10 CHAPTER 1. EMBEDDED SYSTEMS DESIGN

### 1.3. EXAMPLE: KINESIOLOGY AND HEALTH LABORATORY INSTRUMENTATION 11

**Figure 1.5:** Small scale test circuit for the KNH arrays. The input voltage is compared against a bank of threshold detectors, each set to a different fraction of the supply voltage. As the input voltage is increased, more LEDs will illuminate. This is commonly referred to as a rain gage indicator. The threshold detector configuration will be discussed, in detail, later in the book.

**Implement Prototype and Testing.** The circuit was then implemented on a powered, prototype board to ensure correct operation. The circuit was slowly brought online, a subsystem at a time, starting from the lowest level of the structure chart. Each subsystem was implemented and tested as it was brought online.

Once the array was completely prototyped and tested, the design was converted over to a printed circuit board (PCB) layout. The PCB was assembled and tested to ensure proper operation. The PCB circuit was tested against the prototyped circuit.

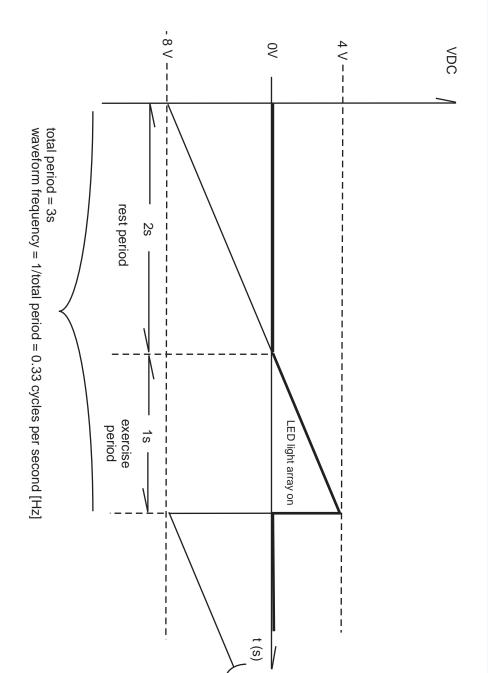

With the circuit correctly operating, it was installed in an aluminum chassis and delivered to the Kinesiology and Health Department. The research team then tested the array panel under actual laboratory conditions. As a result of the testing, several circuit modifications were required to allow a "programmable" rest and exercise period for the desired exertion array. As shown in Figure 1.7, any rest period and exercise period may be selected by careful choice of the signal parameters applied to the desired exertion array. In the example shown, a rest period of 2s and an exercise period of 1s was desired. The signal generator was set for a ramp signal with the parameters shown. The input protection circuitry limits the excursion of the input signal to approximately 0 to 4 volts.

**Figure 1.6:** Circuit diagram for the KNH arrays. (left) Actual exertion array and (right) desired exertion array.

as input voltage increases in response to signal generator input signal. The input to the array is protected by a 4.7 VDC zener diode and a Schottky diode to limit voltage input to levels between approximately 0 and 4.7 VDC. Figure 1.7: KNH array settings. LEDs will illuminate for input voltages between 0 and 4 VDC. More LEDs, incrementally, illuminate

### 1.4 SUMMARY

In this chapter, we discussed the design process, related tools, and applied the process to a real world design. As previously mentioned, this design example will be periodically revisited throughout the text. It is essential to follow a systematic, disciplined approach to embedded systems design to successfully develop a prototype that meets established requirements.

### **1.5 CHAPTER PROBLEMS**

- **1.1.** What is an embedded system?

- 1.2. What aspects must be considered in the design of an embedded system?

- 1.3. What is the purpose of the structure chart, UML activity diagram, and circuit diagram?

- **1.4.** Why is a system design only as good as the test plan that supports it?

- **1.5.** During the testing process, when an error is found and corrected, what should now be accomplished?

- 1.6. Discuss the top-down design, bottom-up implementation concept.

- **1.7.** Describe the value of accurate documentation.

- **1.8.** What is required to fully document an embedded systems design?

- **1.9.** Calculate the signal parameters required to drive the KNH array with a 1s rest time and a 2s exercise time.

- **1.10.** What is the purpose of the input protection circuitry for the desired exertion array in the KNH panel?

### REFERENCES

M. Anderson, Help Wanted: Embedded Engineers Why the United States is losing its edge in embedded systems, *IEEE-USA Today's Engineer*, Feb 2008.

S. Barrett and D. Pack "Microcontroller Fundamentals for Engineers and Scientists," Morgan & Claypool, 2006.

M. Fowler, "UML Distilled: A Brief Guide to the Standard Object Modeling Language," Addison Wesley, 2000.

M. Page Jones, "The Practical Guide to Structured Systems Design," Yourdon Press, 1988.

### CHAPTER 2

# Atmel AVR Architecture Overview

Objectives: After reading this chapter, the reader should be able to

- Provide an overview of the RISC architecture of the ATmega164.

- Describe the different ATmega164 memory components and their applications.

- Explain the ATmega164 internal subsystems and their applications.

- Highlight the operating parameters of the ATmega164.

- Summarize the special ATmega164 features.

### 2.1 ATMEGA164 ARCHITECTURE OVERVIEW

In this section, we describe the overall architecture of the Atmel AVR ATmega164. We begin with an introduction to the concept of the Reduced Instruction Set Computer (RISC) and briefly describe the Atmel Assembly Language Instruction Set. A brief introduction of the assembly language is warranted since we will be programming mainly in C throughout the book. <sup>1</sup> We then provide a detailed description of the ATmega164 hardware architecture.

### 2.1.1 REDUCED INSTRUCTION SET COMPUTER—RISC

A microcontroller is an entire computer system contained within a single integrated circuit or chip. Microcontroller operation is controlled by a user-written program interacting with the fixed hardware architecture resident within the microcontroller. A specific microcontroller architecture can be categorized as either accumulator-based, register-based, stack-based, or a pipeline architecture.

The Atmel ATmega164 is a register-based architecture. In this type of architecture, all operands of an operation are stored in registers collocated with the central processing unit (CPU). This means that before an operation is performed, the computer loads all necessary data for the operation to its CPU. The result of the operation is also stored in a register. During program execution, the CPU interacts with the register set and minimizes slower memory accesses. Memory accesses are typically handled as background operations.

Coupled with the register-based architecture is an instruction set based on the RISC concept. A RISC processor is equipped with a complement of very simple and efficient basic operations. More

<sup>&</sup>lt;sup>1</sup>We want to emphasize the importance of understanding the assembly language programming language; however, especially for implementing applications that are time critical.

### 16 CHAPTER 2. ATMEL AVR ARCHITECTURE OVERVIEW

complex instructions are built up from these very basic operations. This allows for efficient program operation. The Atmel ATmega164 has 131 RISC type instructions. Most can be executed in a single clock cycle. The main objective of the RISC processor is to simplify hardware and instructions for the purpose of increasing the overall performance of the computer. The ATmega164 is also equipped with additional hardware to allow for the multiplication operation in two clock cycles. In many other microcontroller architectures, multiplication typically requires many more clock cycles. For additional information on the RISC architecture, the interested reader is referred to Hennessy and Patterson.

The Atmel ATmega164 is equipped with 32 general purpose 8-bit registers that are tightly coupled to the processor's arithmetic logic unit (ALU) within the CPU. The processor is designed following the Harvard Architecture format, as it is equipped with separate, dedicated memories and buses for program and data information. The register-based Harvard Architecture, coupled with the RISC-based instruction set, allows for fast and efficient program execution and allows the processor to complete an assembly language instruction every clock cycle. Atmel indicates the ATmega164 can execute 20 million instructions per second (MIPS) when operating at the maximum clock speed of 20 MHz (Atmel).

### 2.1.2 ASSEMBLY LANGUAGE INSTRUCTION SET

An instruction set is a group of instructions a machine "understands" to execute. A large number of instructions provide flexibility but requires more complex hardware. Thus, an instruction set is unique for a given hardware and can not be used with another hardware configuration. Atmel has equipped the ATmega164 with 131 different instructions. Most of these instructions are executed in a single clock cycle.

For the most efficient and fast execution of a given microcontroller, assembly language should be employed. Assembly language is written to efficiently interact with a specific microcontroller's resident hardware. To effectively use the assembly language, the programmer must be thoroughly familiar with the low-level architecture details of the controller. Furthermore, the learning curve for a given assembly language is quite steep, and lessons learned do not always transfer to another microcontroller. For these reasons, we will program the Atmel ATmega164 using the C language throughout the text. The C programming language allows for direct control of microcontroller hardware at the register level while being portable to other microcontrollers in the AVR line. When a C program is compiled during the software development process, the program is first converted to assembly language and then to the machine code for the specific microcontroller.

We must emphasize that programming in C is not better than assembly language or vice versa. Both approaches have their inherent advantages and disadvantages. We have chosen to use C in this book for, the reasons previously discussed. Throughout this book, we will use the ImageCraft ICC AVR compiler for our coding examples (ImageCraft). The specific features discussed are also available on other Atmel AVR C compilers.

### 2.1. ATMEGA164 ARCHITECTURE OVERVIEW 17

### 2.1.3 C OPERATOR SIZE

When declaring a variable in C, the number of bits used to store the operator is also indirectly specified. In Figure 2.1, we provide a list of common C variable sizes used with the ImageCraft ICC AVR compiler. The size of other variables such as pointers, shorts, longs, etc., are contained in the compiler documentation (ImageCraft).

| Туре          | Size | Range                    |

|---------------|------|--------------------------|

| unsigned char | 1    | 0255                     |

| signed char   | 1    | -128127                  |

| unsigned int  | 2    | 065535                   |

| signed int    | 2    | -3276832767              |

| float         | 4    | +/-1.175e-38 +/-3.40e+38 |

| double        | 4    | +/-1.175e-38 +/-3.40e+38 |

Figure 2.1: C variable sizes used with the ImageCraft ICC AVR compiler.

When programming microcontrollers, it is important to know the number of bits used to store the variable and also where the variable will be assigned. For example, assigning the contents of an unsigned char variable, which is stored in 8-bits, to an 8-bit output port will have a predictable result. However, assigning an unsigned int variable, which is stored in 16-bits, to an 8-bit output port does not provide predictable results. It is wise to insure your assignment statements are balanced for accurate and predictable results. Recall the modifier "unsigned" indicates all bits will be used to specify the magnitude of the argument. Signed variables will use the left most bit to indicate the polarity  $(\pm)$  of the argument.

### 2.1.4 BIT TWIDDLING

It is not uncommon, in embedded system design projects, to have every pin on a microcontroller employed. Furthermore, it is not uncommon to have multiple inputs and outputs assigned to the same port but on different port input/output pins. Some compilers support specific pin reference.

Another technique that is not compiler specific is bit twiddling. Figure 2.2 provides bit twiddling examples on how individual bits may be manipulated without affecting other bits. The information provided here was extracted from the ImageCraft ICC AVR compiler documentation (ImageCraft).

| Syntax | Description          | Example                                             |

|--------|----------------------|-----------------------------------------------------|

| a   b  | bitwise or           | PORTA $\models$ 0x80; // turn on bit 7 (msb)        |

| a & b  | bitwise and          | if ((PINA & $0x81$ ) == 0) // check bit 7 and bit 0 |

| a ^ b  | bitwise exclusive or | PORTA ^= 0x80; // flip bit 7                        |

| ~a     | bitwise complement   | PORTA &= $\sim 0x80$ ; // turn off bit 7            |

Figure 2.2: Bit twiddling (ImageCraft).

#### 2.1.5 ATMEGA164 ARCHITECTURE OVERVIEW

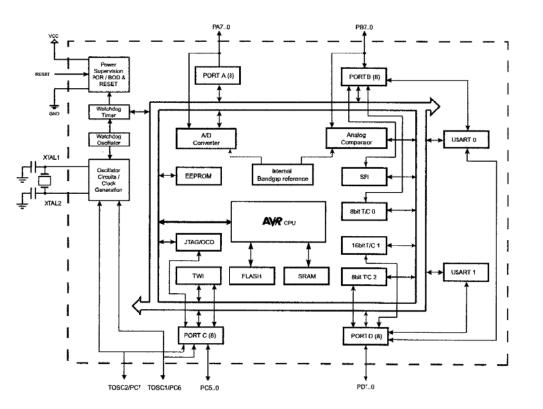

We have chosen the ATmega164 as a representative of the Atmel AVR line of microcontrollers. Lessons learned with the ATmega164 may be easily adapted to all other processors in the AVR line. A block diagram of the Atmel ATmega164's architecture is shown in Figure 2.3.

As can be seen from the figure, the ATmega164 has external connections for power supplies (VCC, GND), external time base input pins to drive its clocks (XTAL1 and XTAL2), processor reset (active low RESET), and four 8-bit ports (PA0-PA7, PB0-PB7, PC0-PC7, and PD0-PD7), which are use to interact with the external world. As we shall soon see, these ports, may be used as general purpose digital input/output ports, or they may be used for the alternate functions. The ports are interconnected with the ATmega164's CPU and internal subsystems via internal buses. The ATmega164 also contains a timer subsystem, an analog-to-digital converter, an analog comparator, an interrupt subsystem, a timing subsystem, memory components, and extensive serial communication features (Atmel).

In the next several subsections, we briefly describe each of these internal subsystems shown in the figure. Detailed descriptions of major subsystem operation and programming are provided later in this book. We can not cover all features of the microcontroller due to limited space.

#### 2.2. NONVOLATILE AND DATA MEMORIES 19

Figure 2.3: Atmel AVR ATmega164 Block Diagram. (Figure used with permission of Atmel, Incorporated.)

## 2.2 NONVOLATILE AND DATA MEMORIES

The ATmega164 is equipped with three main memory sections: flash electrically erasable programmable read only memory (EEPROM), byte-addressable EEPROM for data storage, and static random access memory (SRAM). We discuss each memory component in turn, next.

#### 2.2.1 IN-SYSTEM PROGRAMMABLE FLASH EEPROM

Flash EEPROM is nonvolatile: memory contents are retained when microcontroller power is lost. Flash EEPROM is used to store programs. It is called bulk programmable since it can be erased and programmed as a single unit. Also, should a program require a large table of constants, it may be included as a global variable within a program and programmed into flash EEPROM with the rest of the program. The ATmega164 is equipped with 16K bytes of onboard reprogrammable flash memory. This memory component is organized into 8K locations with 16 bits at each location.

The flash EEPROM is in-system programmable. In-system programmability means the microcontroller can be programmed while resident within a circuit. It does not have to be removed from the circuit, as was the case for older EEPROM technologies, for programming. Instead, a host personal computer (PC) connected via a cable to a microcontroller downloads the program directly to the microcontroller. Alternately, the microcontroller can be programmed outside of its resident circuit using a flash programmer board. We will use this technique throughout the book since many of our examples will use the microcontroller pins required for ISP programming. Specifically, we will use the Atmel STK500 AVR Flash MCU Starter Kit for programming the ATmega164. This inexpensive development board (less than \$100) is readily available from a number of suppliers.

The flash EEPROM is used to bulk store application programs for execution. Another type of onboard EEPROM is the byte-addressable type. It is used to store variables needed by the system even in the event of a power failure. We discuss this type of memory next.

#### 2.2.2 BYTE-ADDRESSABLE EEPROM

Byte-addressable memory is used to permanently store and recall variables during program execution. It, too, is nonvolatile. It is especially useful for logging system malfunctions and fault data during program execution. It is also useful for storing data that must be retained during a power failure but might need to be changed periodically. Examples where this type of memory is used are found in applications to store system parameters, electronic lock combinations, and automatic garage door electronic unlock sequences. The ATmega164 is equipped with 512 bytes of EEPROM.

#### 2.2.3 ACCESSING BYTE-ADDRESSABLE EEPROM EXAMPLE

In this section, we describe how to read from and write to the byte-addressable EEPROM aboard the ATmega164. As previously mentioned, the features of the ImageCraft ICC AVR compiler will be used to access the memory. Other compilers have similar features.

To configure a program to access byte-addressable EEPROM memory, the following steps must be accomplished:

1. The compiler specific support function definitions for accessing EEPROM must be included within the main C program. Using the ImageCraft ICC AVR compiler, this is accomplished by including the header file **eeprom.h** as shown below:

//EEPROM support functions

#include<eeprom.h>

2. The variables to be placed in EEPROM must be declared as global variables. For the Image-Craft ICC AVR compiler, this is accomplished using the #pragma construct illustrated below. Other variables to be stored in EEPROM would be included between the two #pragma statements. Also, a normal global variable is declared to correspond to the EEPROM based variable to facilitate reading from and writing to the variable from the EEPROM location. In the fol-

#### 2.2. NONVOLATILE AND DATA MEMORIES 21

lowing example, the variable residing in EEPROM is called "test\_data\_EEPROM" while the corresponding variable used within the program is called "test\_data."

#pragma data: eeprom

unsigned int test\_data\_EEPROM = 0x1234;

#pragma data:data

//global variables

unsigned int test\_data;

3. The EEPROM variable may then be written to, or read from, a byte-addressable EEPROM memory location using the following ICC AVR compiler specific function calls.

EEPROM\_READ((int) &test\_data\_EEPROM, test\_data);

EEPROM\_WRITE((int)&test\_data\_EEPROM, test\_data);

When a program containing byte-addressable EEPROM variables is compiled, a < \*.eep > file is generated in addition to the < \*.hex > file. The < \*.eep > file is used to, initially, configure the EEPROM when the ATmega164 is programmed using the STK500. The STK500 may also be used to read the contents of the EEPROM.

#### 2.2.4 STATIC RANDOM ACCESS MEMORY (SRAM)

Static RAM memory is volatile. That is, if the microcontroller loses power, the contents of SRAM memory are lost. It can be written to, and read from, during program execution. The ATmega164 is equipped with 1K (actually 1120) bytes of SRAM. A small portion (96 locations) of the SRAM is set aside for the general purpose registers used by the CPU and also for the input/output and peripheral subsystems aboard the microcontroller. A complete ATmega164 register listing and accompanying header file are provided in Appendices A and B, respectively. During program execution, RAM is used to store global variables, support dynamic memory allocation of variables, and to provide a location for the stack.

#### 2.2.5 PROGRAMMABLE LOCK BITS

To provide users with memory security from tampering, the ATmega164 is equipped with six memory lock bits. These lock bits are programmed using the Atmel STK500 programming board. The lock bits may be configured for the following options:

- No memory lock features enabled,

- No further programming of memory is allowed using parallel or serial programming techniques, or

• No further programming or verification of memory is allowed using parallel or serial programming techniques.

The machine code contents of Flash or byte-addressable EEPROM memory may be read using an STK500 and the AVR Studio software. If one tries to read the contents of Flash memory with the lock bits set for the highest level of security, default memory values are displayed.

## 2.3 PORT SYSTEM

The Atmel ATmega164 has four, 8-bit general purpose, digital input/output (I/O) ports designated PORTA, PORTB, PORTC, and PORTD. All of these ports also have alternate functions, which will be described later. In this section, we concentrate on the basic digital I/O port features.

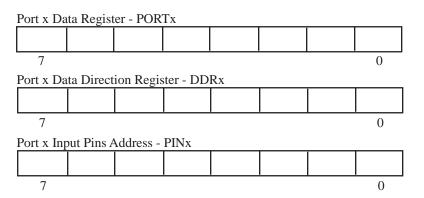

As shown in Figure 2.4, each port has three registers associated with it.

- Data Register PORTx —- used to write output data to the port.

- Data Direction Register DDRx —- used to set a specific port pin to either output (1) or input (0).

- Input Pin Address PINx --- used to read input data from the port.

Figure 2.4(b) describes the settings required to configure a specific port pin to either input or output. If selected for input, the pin may be selected for either an input pin or to operate in the high impedance (Hi-Z) mode. In Hi-Z mode, the input appears as high impedance to a particular pin. If selected for output, the pin may be configured further for either logic low or logic high.

Port pins are usually configured at the beginning of a program for either input or output, and their initial values are then set. Usually, all eight pins for a given port are configured simultaneously. A code example is provided below to show how ports are configured. Note that since we are using the C programming language with a compiler include file, the register contents are simply referred to by name. Note that the data direction register (DDRx) is first used to set the pins as either input or output, and then the data register (PORTx) is used to set the initial value of the output port pins. Any pins not used in a specific application should be configured as output pins since an unused pin configured as an input can be a source for noise to enter the processor.

```

void initialize_ports(void)

{

DDRA=Oxfc; //set PORTA[7:2] as output, PORTA[1:0] as input (1111_1100)

PORTA=Ox03; //initialize PORTA[7:2] low

```

#### 2.3. PORT SYSTEM 23

a) port associated registers

| DDxn | PORTxn | I/O    | Comment                                 | Pullup |

|------|--------|--------|-----------------------------------------|--------|

| 0    | 0      | input  | Tri-state (Hi-Z)                        | No     |

| 0    | 1      | input  | source current if externally pulled low | Yes    |

| 1    | 0      | output | Output Low (Sink)                       | No     |

| 1    | 1      | output | Output High (Source)                    | No     |

x: port designator (A, B, C, D) n: pin designator (0 - 7)

b) port pin configuration

Figure 2.4: ATmega164 port configuration registers.

DDRB=0xa0; //PORTB[7:4] as output, set PORTB[3:0] as input PORTB=0x00; //disable PORTB pull-up resistors DDRC=0xff; //set PORTC as output PORTC=0x00; //initialize low DDRD=0xff; //set PORTD as output PORTD=0x00; //initialize low }

To read the value from a port pin configured as input, the following code could be used. Note the variable used to read the value from the input pins is declared as an unsigned char since both the port and this variable type are eight bits wide.

```

unsigned char new_PORTB; //new values of PORTB

:

.

.

new_PORTB = PINB; //read PORTB

```

## 2.4 PERIPHERAL FEATURES—INTERNAL SUBSYSTEMS

In this section, we provide a brief overview of the peripheral features of the ATmega164. It should be emphasized that these features are the internal subsystems contained within the confines of the microcontroller chip. These built-in features allow complex and sophisticated tasks to be accomplished by the microcontroller.

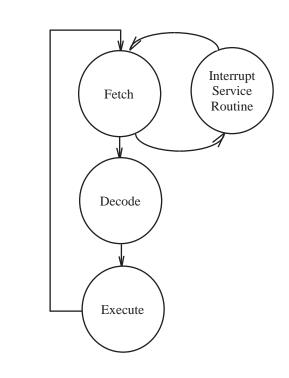

#### 2.4.1 TIME BASE

The microcontroller is a complex synchronous state machine. It responds to program steps in a sequential manner as dictated by a user-written program. The microcontroller sequences through a predictable fetch-decode-execute sequence. Each program instruction issues a series of signals to control the microcontroller hardware to accomplish instruction related operations.

The speed at which a microcontroller sequences through these actions is controlled by a precise time base called the clock. The clock source is routed throughout the microcontroller to provide a time base for all peripheral subsystems. The ATmega164 may be clocked internally using a user-selectable resistor capacitor (RC) time base, or it may be clocked externally. The RC internal time base is selected using programmable fuse bits. We will discuss how to do this in the application section of this chapter. You may choose an internal fixed clock operating frequency of 1, 2, 4 or 8 MHz.

To provide for a wider range of frequency selections, an external time source may be used. The external time sources, in order of increasing accuracy and stability, are an external RC network, a ceramic resonator, and a crystal oscillator. The system designer chooses the time base frequency and clock source device appropriate for the application at hand. As previously mentioned, the maximum operating frequency of the ATmega164P with a 5 VDC supply voltage is 20 MHz.

#### 2.4.2 TIMING SUBSYSTEM

The ATmega164 is equipped with a complement of timers which allows a user to generate a precision output signal, measure the characteristics (period, duty cycle, frequency) of an incoming digital

#### 2.4. PERIPHERAL FEATURES—INTERNAL SUBSYSTEMS 25

signal, generate precision delays, implement a real time clock, or count external events. Specifically, the ATmega164 is equipped with two 8-bit timer/counters and one 16-bit counter. We discuss the operation, programming, and application of the timing system in Chapter 6.

#### 2.4.3 PULSE WIDTH MODULATION CHANNELS

A pulse width modulated or PWM signal is characterized by a fixed frequency and a varying duty cycle. A duty cycle is defined as the percentage of time a periodic signal is logic high over the signal period. It may be formally expressed as:

#### $duty cycle[\%] = (on time/period) \times (100\%)$

The ATmega164 is equipped with three separate timers to support six channels of pulse width modulation (PWM) operation. The PWM channels coupled with the flexibility of dividing the time base down to different PWM subsystem clock source frequencies allow a user to configure the microcontroller to generate a wide variety of PWM signals: from relatively high frequency low duty cycle signals to relatively low frequency high duty cycle signals.

PWM signals are used in a wide variety of applications including controlling the position of a servo motor, DC motor speed control, or generating an analog DC output signal. We discuss the operation, programming, and application of the PWM system in Chapter 6.

#### 2.4.4 SERIAL COMMUNICATIONS

The ATmega164 is equipped with a host of different serial communication subsystems including the Universal Synchronous and Asynchronous Serial Receiver and Transmitter (USART), the serial peripheral interface (SPI), and the Two-wire Serial Interface. What all of these systems have in common is the serial transmission of data. In a serial communications transmission scheme, data are sent a single bit at a time from transmitter to receiver.

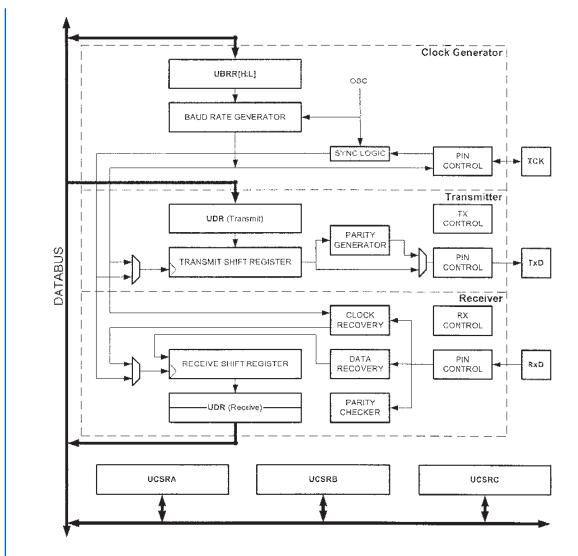

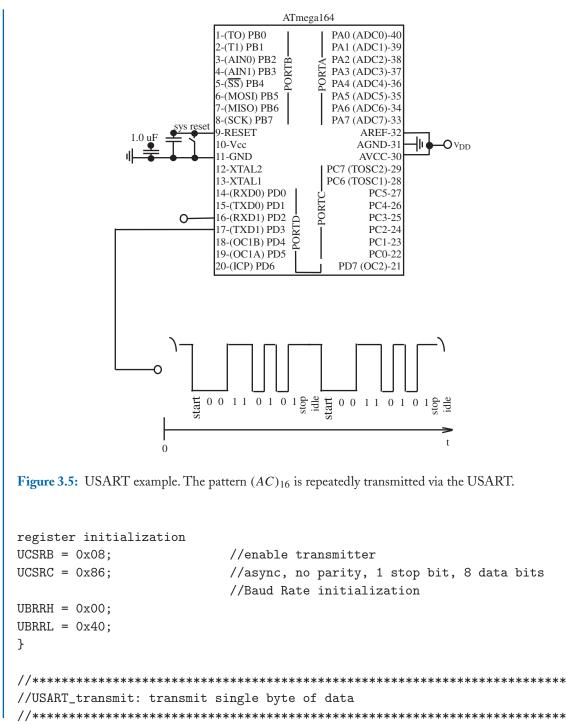

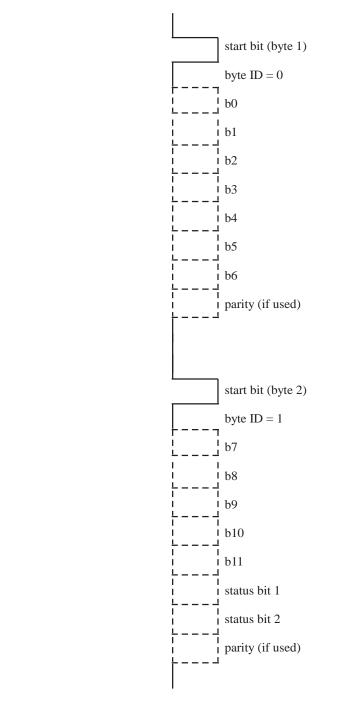

#### 2.4.4.1 Serial USART

The serial USART is used for full duplex (two way) communication between a receiver and a transmitter. This is accomplished by equipping the ATmega164 with independent hardware for the transmitter and receiver pair. The USART is typically used for asynchronous communication. That is, there is not a common clock between the transmitter and the receiver to keep them synchronized with one another. To maintain synchronization between the transmitter and receiver, framing start and stop bits are used at the beginning and end of each data byte in a transmission sequence.

The ATmega164 USART is quite flexible. It has the capability to be set to a variety of data transmission rates known as the Baud (bits per second) rate. The USART may also be set for data bit widths of 5 to 9 bits with one or two stop bits. Furthermore, the ATmega164 is equipped with a hardware generated parity bit (even or odd) and parity check hardware at the receiver. A single parity bit allows for the detection of a single bit error within a byte of data. The USART may also be configured to operate in a synchronous mode. We discuss the operation, programming, and application of the USART in Chapter 3.

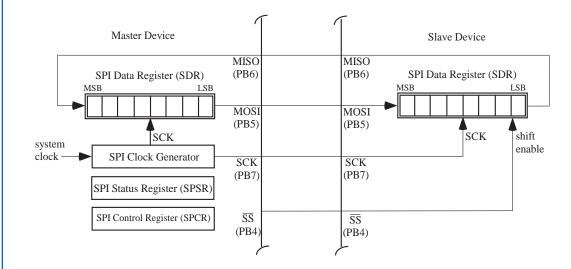

#### 2.4.4.2 Serial Peripheral Interface—SPI

The ATmega164 Serial Peripheral Interface (SPI) can also be used for two-way serial communication between a transmitter and a receiver. In the SPI system, the transmitter and the receiver must share a common clock source. This requires an additional clock line between the transmitter and the receiver but allows for higher data transmission rates as compared to the USART.

The SPI may be viewed as a synchronous 16-bit shift register with an 8-bit half residing in the transmitter and the other 8-bit half residing in the receiver. The transmitter is designated as the master since it is providing the synchronizing clock source between the transmitter and the receiver. The receiver is designated as the slave. We discuss the operation, programming, and application of the SPI in Chapter 3.

#### 2.4.4.3 Two-wire Serial Interface—TWI

The TWI subsystem allows the system designer to network a number of related devices (microcontrollers, transducers, displays, memory storage, etc.) together into a system using a two wire interconnecting scheme. The TWI allows a maximum of 128 devices to be connected together. Each device has its own unique address and may both transmit and receive over the two wire bus at frequencies up to 400 kHz. This allows the device to freely exchange information with other devices in the network within a small area (Atmel).

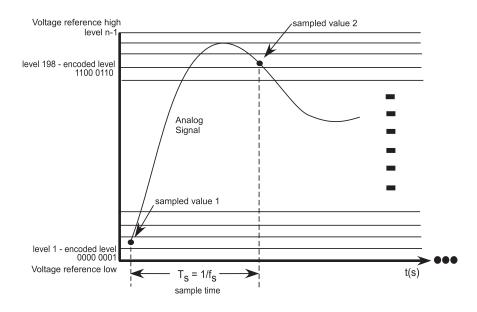

#### 2.4.5 ANALOG TO DIGITAL CONVERTER—ADC

To interact with external analog signals, the ATmega164 is equipped with an eight channel analog to digital converter (ADC) subsystem. The ADC converts an analog signal from the outside world into a binary representation suitable for use by the microcontroller. The ATmega164 ADC has 10 bit resolution, which means that an analog voltage between 0 and 5 will be encoded into one of 1024 binary representations between  $(000)_{16}$  and  $(3FF)_{16}$ . This provides the ATmega164 with a voltage resolution of approximately 4.88 mV. We discuss the operation, programming, and application of the ADC in Chapter 4 (Atmel).

#### 2.4.6 ANALOG COMPARATOR

The ATmega164 is equipped with an analog comparator. An analog comparator may be used as a threshold detector or used to clean up a corrupted digital signal. The analog comparator has two external inputs designated AIN0 and AIN1. When the voltage at AIN0 is greater than the voltage at AIN1, the output of the comparator, AC0, is set to logic one (Atmel).

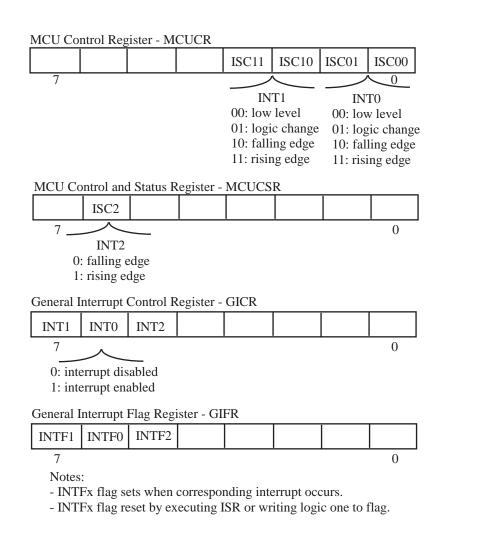

#### 2.4.7 INTERRUPTS

The normal execution of a program is performed by following a designated sequence of instruction execution. However, sometimes this normal sequence of instructions must be interrupted to respond to higher priority events inside and outside the microcontroller. When these higher priority events occur, the microcontroller must temporarily suspend normal operation and execute event specific

#### 2.4. PERIPHERAL FEATURES—INTERNAL SUBSYSTEMS 27

actions called an interrupt service routine. Once the higher priority event has been serviced, the microcontroller returns and continues to operate normally.

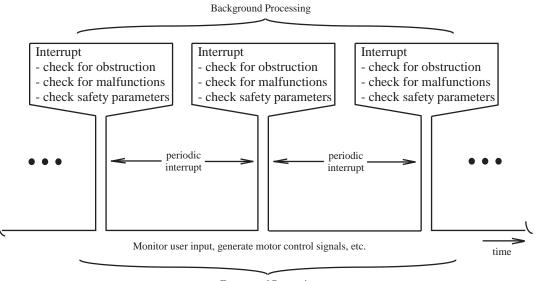

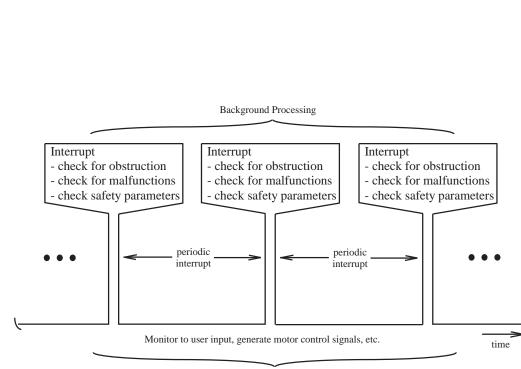

Interrupts may also be employed to continuously monitor the status of an ongoing event while the microcontroller is processing other activities. For example, a microcontroller controlling access for an electronic door must monitor input commands from a user and generate the appropriate PWM signal to open and close the door. Once the door is in motion, the controller must monitor door motor operation for obstructions, malfunctions, and other safety related parameters. This may be accomplished using interrupts. In this example, the microcontroller is responding to user input status in the foreground while monitoring safety related status in the background using interrupts as illustrated in Figure 2.5.

Foreground Processing

**Figure 2.5:** Interrupt used for background processing. The microcontroller responds to user input status in the foreground while monitoring safety related status in the background using interrupts.

The ATmega164 is equipped with mechanisms to detect a complement of 31 interrupt sources. Three of the interrupts are provided for external interrupt sources while the remaining 29 interrupts support the efficient operation of peripheral subsystems aboard the microcontroller (Atmel). We discuss the operation, programming, and application of the interrupt system in Chapter 5.

## 2.5 PHYSICAL AND OPERATING PARAMETERS

In this section, we provide data on the physical layout and operating parameters of the ATmega164 microcontroller. As a system designer, it is important to know the various physical and operating parameter options available to select the best option for a given application.

### 2.5.1 PACKAGING

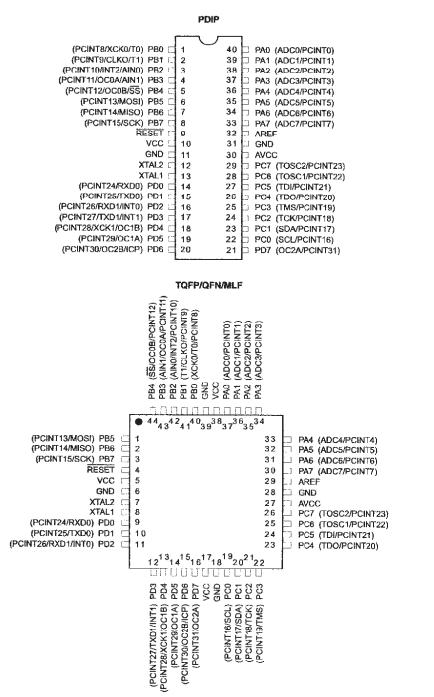

The ATmega164 comes in a variety of different packaging styles: a 40-pin plastic dual in line package (PDIP), a 44-lead thin quad flat pack (TQFP) package, a 44-pad quad flat non-lead/micro lead frame (QFN/MLF) package, and a 44 pin DRQFN package. The pinout diagram for the PDIP and the TQFP/QFN/MLF packaging options are shown in Figure 2.6 (Atmel).

#### 2.5.2 POWER CONSUMPTION

The ATmega164 operates at supply voltages from 1.8 to 5.5 VDC. In the application examples that follow, we will use a standard laboratory 5 VDC power supply but also discuss a method of providing a 5 VDC supply using an off-the-shelf 9 VDC battery. The current draw for the microcontroller is quite low. For example, when the ATmega164 is actively operating at 1 MHz from a 1.8 VDC power source, the current draw is 0.4 mA. When placed in the power-down mode, the microcontroller will draw less than 0.1 microamp of current from the voltage source.

#### 2.5.3 SPEED GRADES

The ATmega164 operates with a clock speed from 0 to 20 MHz. As previously discussed, the operating speed of the microcontroller is set by the time base chosen for the processor. Since faster microcontroller operation is not always the best option, the system designer must determine the optimal speed of microcontroller operation for a given application. The microcontroller's power consumption is directly related to operating speed. That is, the faster the operating speed of the microcontroller the higher its power consumption. This becomes especially critical in portable, battery-operated embedded systems applications.

That completes our brief introduction to the features of the ATmega164. In the next section, we discuss how to choose a specific microcontroller for a given application.

## 2.6 CHOOSING A MICROCONTROLLER

To choose a specific microcontroller for a given application, the following items must be considered:

- The microcontroller must have the specific subsystems required by the application. For example, does the application require analog-to-digital conversion, serial communications, etc.?

- How many digital input/output pins are required by the controller?

- How much Flash EEPROM memory is required by the application?

#### 2.6. CHOOSING A MICROCONTROLLER 29

**Figure 2.6:** Atmel AVR ATmega164 Pinout Diagram: a) 40-pin PDIP, b) TQFP/QFN/MFL (Figure used with permission of Atmel, Incorporated.)

To answer these questions, it is helpful to construct a diagram illustrating all peripheral devices and their connection to the microcontroller. This will help to determine the required microcontroller subsystems and the number of digital input/output pins.

The memory question is more difficult to answer. How can you determine the size of Flash EEPROM required for a specific application before you write the code for the application? In this case, you can choose a family of pin-for-pin compatible microcontrollers such as the AT-mega164/324/644. These microcontrollers have similar features and have memory assets of 16K, 32K and 64K, respectively.

An application can be developed starting with the 16K microcontroller. As the application evolves, one can transition to the 32K and 64K as required. When transitioning to another pin-forpin compatible microcontroller, it is essential to use the specific header file for the microcontroller and also ensure that the interrupt numbers have not changed.

## 2.7 APPLICATION: ATMEGA164 TESTBENCH

The purpose of the Testbench is to illustrate the operation of selected ATmega164 subsystems working with various input and output devices. Most importantly, the Testbench will serve as a template to develop your own applications.

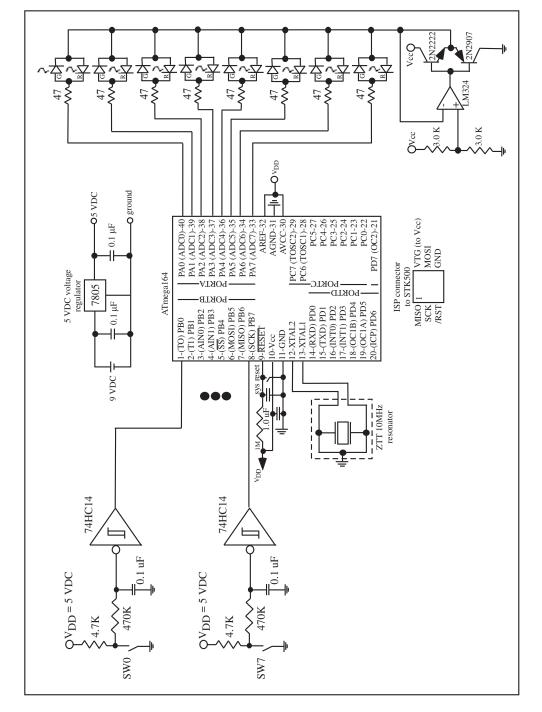

In this section, we provide the hardware configuration of a barebones Testbench and a basic software framework to get the system up and operating. We will connect eight debounced tact switches to PORTB and an eight channel tri-state light emitting diode (LED) array to PORTA. The software will check for a status change on PORTB. When the user depresses one of the tact switches, the ATmega164 will detect the status change, and the corresponding LED on PORTA will transition from red to green.

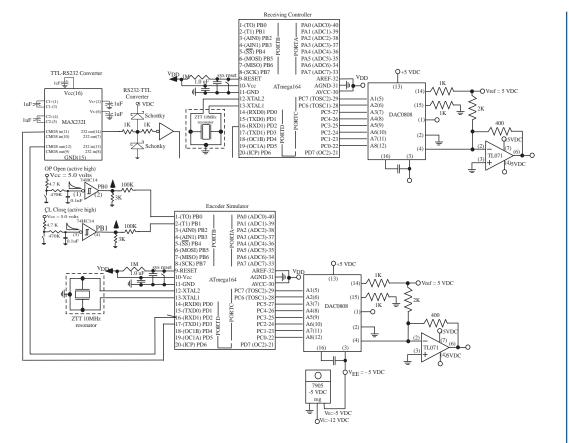

#### 2.7.1 HARDWARE CONFIGURATION

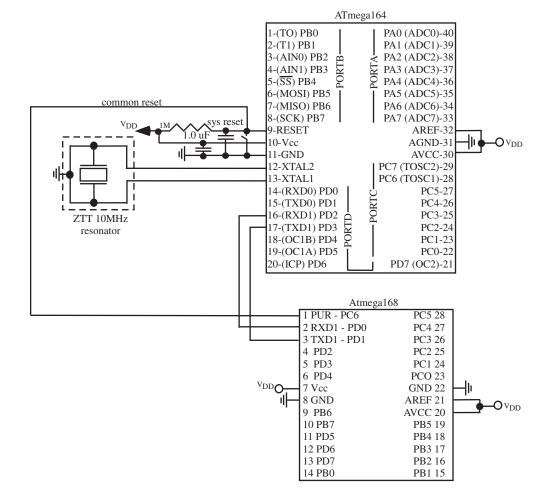

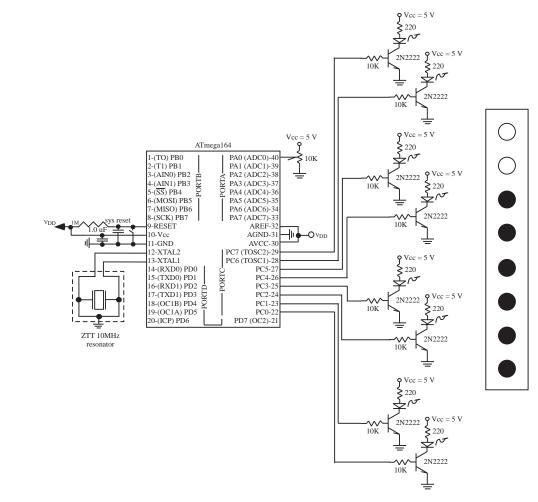

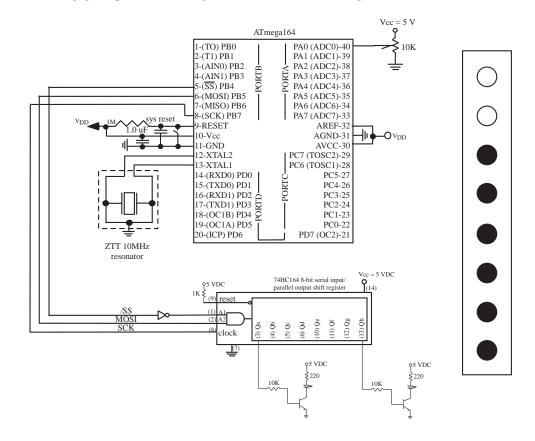

Provided in Figure 2.7 is the basic hardware configuration for the Testbench. We will discuss in detail the operation of the input and output devices in Chapter 7.

PORTA is configured with eight tact (momentary) switches with accompanying debouncing hardware. We discuss the debounce circuit in detail in Chapter 7. PORTB is equipped with an eight channel tri-state LED indicator. For a given port pin, the green LED will illuminate for a logic high, the red LED for a logic low, and no LEDs for a tri-state high-impedance state. We discuss this circuit in detail in Chapter 7.

Aside from the input hardware on PORTB and the output display hardware on PORTA of the controller, there are power (pins 10, 30, 32) and ground (pins 11, 31) connections. A standard 5 VDC power supply may be used for the power connections. For portable applications, a 9 VDC battery equipped with a 5 VDC regulator (LM340-05 or uA7805) may be used as a power source. Pins 9 through 11 have a resistor (1M), two capacitors (1.0 uF), and a tact switch configured to provide a reset switch for the microcontroller. We use a ZTT 10 MHz ceramic resonator as the time base for the Testbench. It is connected to pins 12 (XTAL2) and 13 (XTAL1) of the ATmega164.

#### 2.7. APPLICATION: ATMEGA164 TESTBENCH 31

Figure 2.7: ATmega164 Testbench Hardware.

#### 2.7.2 SOFTWARE CONFIGURATION

The Testbench software is provided below. The program contains the following sections:

- Comments.

- Include files —- We have included the ImageCraft ICC AVR include file for the ATmega164 (iom164v.h). This file provides the software link between the names of the ATmega164 hard-ware registers and the actual hardware locations. When a register is used by name in the program, reference is made to the contents of that register.

- Function prototypes.

- · Global variables.

- Main program—We begin the main program by calling the function to initialize the ports and then enter a continuous loop. Within the loop body the ATmega164 monitors for a status change on PORTB. When the user depresses one of the tact switches connected to PORTB, a change of status is detected and the appropriate LED is illuminated on PORTA.

- Function definition.

```

//file name: testbench.c

//function: provides test bench for ATMEL AVR ATmega164 controller

//target controller: ATMEL ATmega164

11

//ATMEL AVR ATmega164 Controller Pin Assignments

//Chip Port Function I/O Source/Dest Asserted Notes

//Pin 1 PBO to active high RC debounced switch

//Pin 2 PB1 to active high RC debounced switch

//Pin 3 PB2 to active high RC debounced switch

//Pin 4 PB3 to active high RC debounced switch

//Pin 5 PB4 to active high RC debounced switch

//Pin 6 PB5 to active high RC debounced switch

//Pin 7 PB6 to active high RC debounced switch

//Pin 8 PB7 to active high RC debounced switch

//Pin 9 Reset

//Pin 10 VDD

//Pin 11 Gnd

//Pin 12 Resonator

//Pin 13 Resonator

//Pin 14 PDO to tristate LED indicator

//Pin 15 PD1 to tristate LED indicator

```

#### 2.7. APPLICATION: ATMEGA164 TESTBENCH 33