# Digital FrequencySynthesis Demystified

6

# Bar-Giora Goldberg

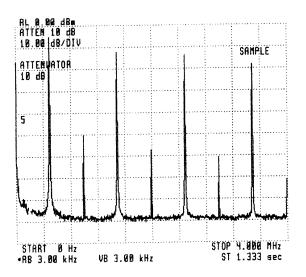

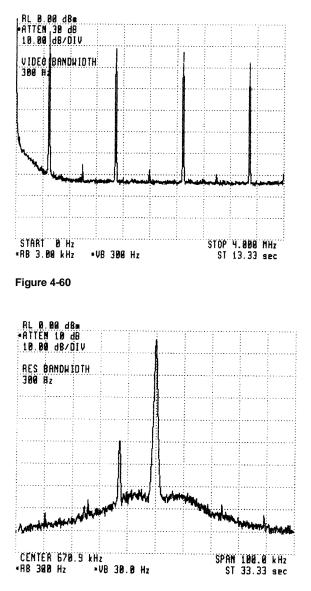

# Digital Frequency Synthesis Demystified

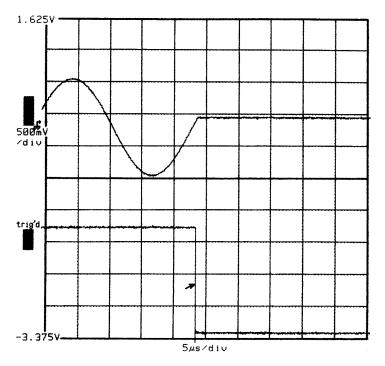

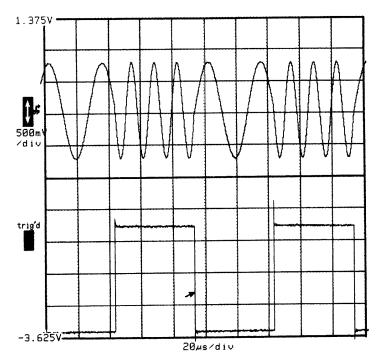

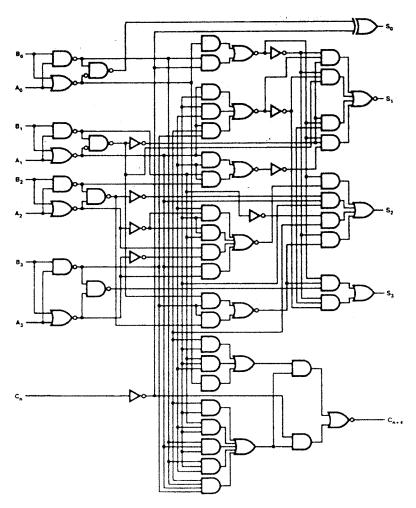

DDS and Fractional-N PLLs

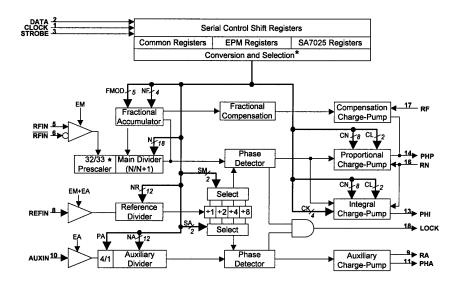

**Bar-Giora Goldberg**

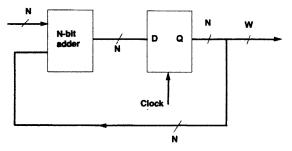

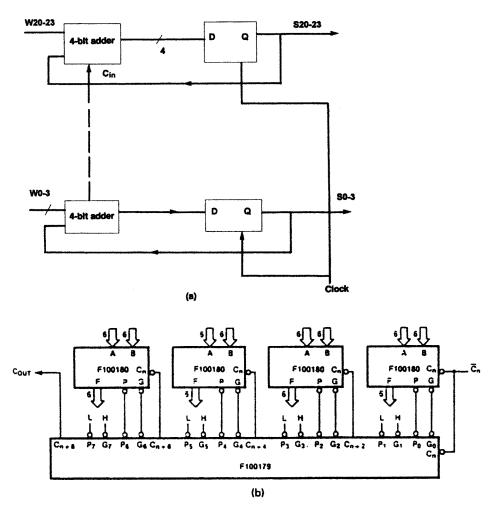

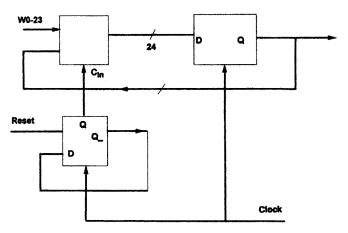

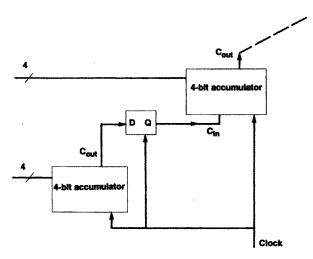

a volume in the Demystified series

Eagle Rock, VA www.LLH-Publishing.com

#### Library of Congress Cataloging-in-Publication Data

Goldberg, Bar-Giora.

Digital frequency synthesis demystified / Bar-Giora Goldberg.

p. cm.

"A volume in the Demystified series."

Includes bibliographical reference and index.

ISBN 1-878707-47-7 (pbk. : alk. paper)

1. Frequency synthesizers--Design and construction. 2. Phase

-locked loops. 3. Digital electronics. I. Title.

TK7872.F73G55 1999

621.3815 486--dc21

99-34856

CIP

Copyright © 1999 by LLH Technology Publishing.

All rights reserved. No part of the book may be reproduced, in any form or means whatsoever, without written permission from the publisher. While every precaution has been taken in the preparation of this book, the publisher and author assume no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

Printed in the United States of America 10 9 8 7 6 5 4 3 2 1

Cover design: Sergio Villareal Developmental Editing: Carol Lewis Production: Kelly Johnson

Eagle Rock, VA www.LLH-Publishing.com To Moshe Shoshana, Pnina, Amit, and Dror

This is a blank page.

# Contents

| Prefaces | xi |

|----------|----|

| Symbols  | xv |

| Chapter 1. Introduction to Frequency Synthesis   | 1  |

|--------------------------------------------------|----|

| 1-1 Introduction and Definitions                 | 1  |

| 1-2 Synthesizer Parameters                       | 5  |

| 1-2-1 Frequency Range                            | 6  |

| 1-2-2 Frequency Resolution                       | 6  |

| 1-2-3 Output Level                               | 7  |

| 1-2-4 Control and Interface                      | 7  |

| 1-2-5 Output Flatness                            | 7  |

| 1-2-6 Output Impedance                           | 7  |

| 1-2-7 Switching Speed                            | 7  |

| 1-2-8 Phase Transient                            | 8  |

| 1-2-9 Harmonics                                  | 9  |

| 1-2-10 Spurious Output                           | 10 |

| 1-2-11 Phase Noise                               | 10 |

| 1-2-12 Standard Reference                        | 13 |

| 1-3 Auxiliary Specifications                     | 13 |

| 1-4 Review of Synthesis Techniques               | 13 |

| 1-4-1 Phase-Locked Loop                          | 14 |

| 1-4-2 Direct Analog Synthesis                    | 21 |

| 1-4-3 Direct Digital Synthesis                   | 26 |

| 1-5 Comparative Analysis                         | 35 |

| 1-6 Conclusion                                   | 37 |

| References                                       | 38 |

| Chapter 2. Frequency Synthesizer System Analysis | 39 |

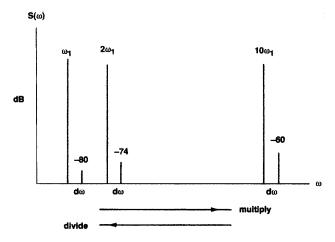

| 2-1 Multiplying and Dividing                     | 39 |

| 2-2 Phase Noise                                  | 42 |

| 2-3 Spurious and Phase Noise in PLL              | 49 |

| 2-4 Phase Noise Mechanism                        | 51 |

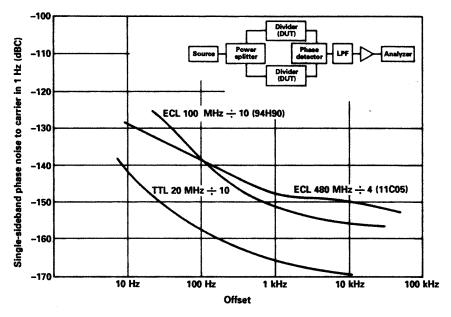

| 2-4-1 Noise in Dividers                          | 51 |

| 2-4-2 Noise in Oscillators                       | 51 |

| 2-4-3 Noise in Phase Detectors                   | 52 |

| 2-5 Mixing and Filtering                         | 53 |

| 2-6 Frequency Planning                           | 55 |

| References                                       | 56 |

|                                                  |    |

| Chapter 3. Measurement Techniques                                | 57         |

|------------------------------------------------------------------|------------|

| 3-1 Switching Speed                                              | 57         |

| 3-2 Phase Noise                                                  | 61         |

| 3-2-1 FM Noise                                                   | 62         |

| 3-2-2 Delay Line Discriminator                                   | 63         |

| 3-2-3 Integrated Phase Noise                                     | 66         |

| 3-2-4 Noise Density                                              | 66         |

| 3-3 Phase Continuity                                             | 66         |

| 3-4 Spurious Signals (Especially DDS)                            | 67         |

| 3-5 Phase Memory                                                 | 69         |

| 3-6 Step Size                                                    | 69         |

| 3-7 Linear FM                                                    | 70         |

| 3-8 Conclusion                                                   | 70         |

| References                                                       | 71         |

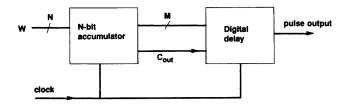

| Chapter 4. DDS General Architecture                              | 73         |

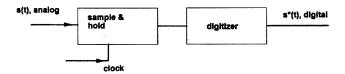

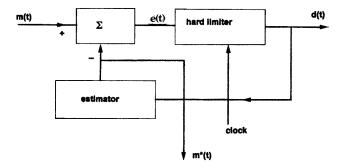

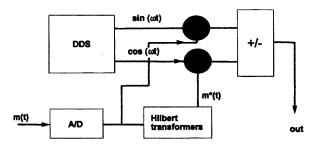

| 4-1 Digital Modulators and Signal Reconstruction                 | 75         |

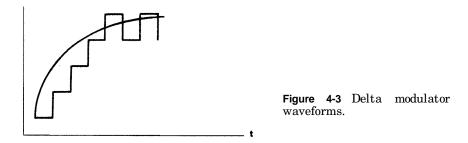

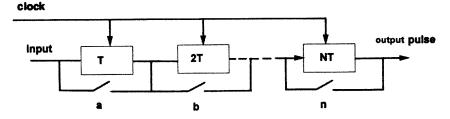

| 4-2 Pulse Output DDS of the First Order                          | 82         |

| 4-3 Pulse Output DDS of the Second Order                         | 87         |

| 4-4 Standard DDS                                                 | 89         |

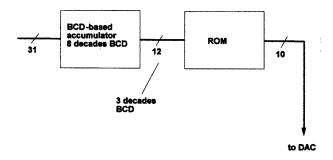

| 4-4-1 Binary-Coded Decimal DDS                                   | 100        |

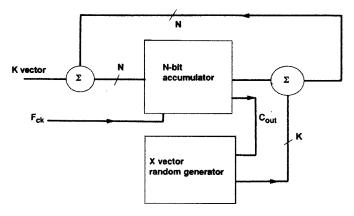

| 4-5 Randomization                                                | 105        |

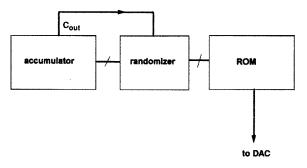

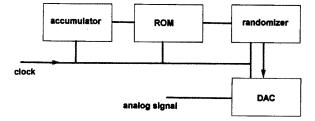

| 4-5-1 Wheatley Procedure                                         | 106        |

| 4-5-2 Randomizing Sine Output                                    | 108        |

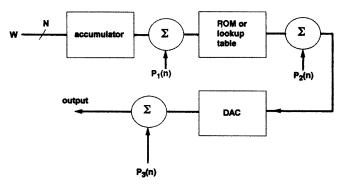

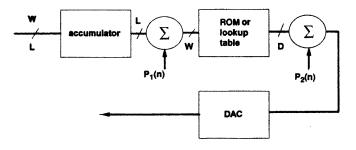

| 4-6 Quantization Errors                                          | 109        |

| 4-6-1 Digitized Model                                            | 109        |

| 4-7 Logic Speed Considerations                                   | 120        |

| 4-8 Modulation                                                   | 120        |

| 4-9 State-of-the-Art Components and Systems                      | 128        |

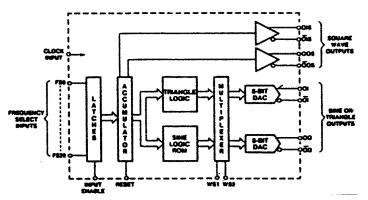

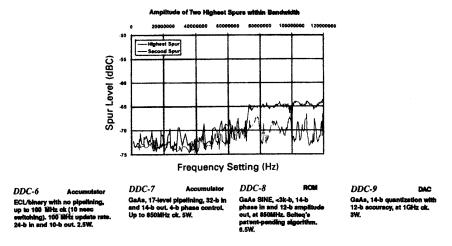

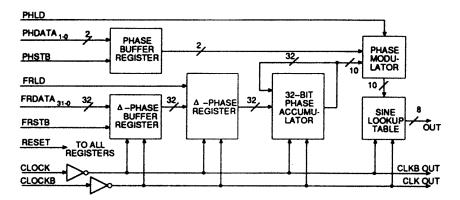

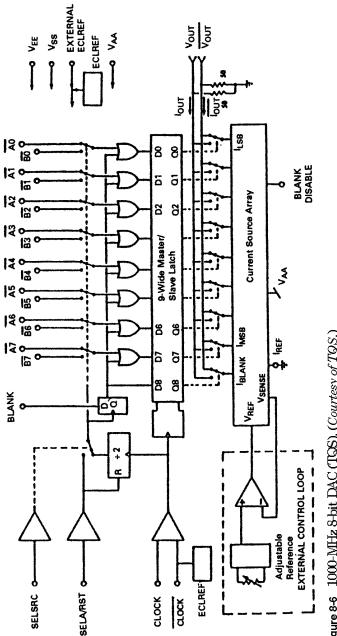

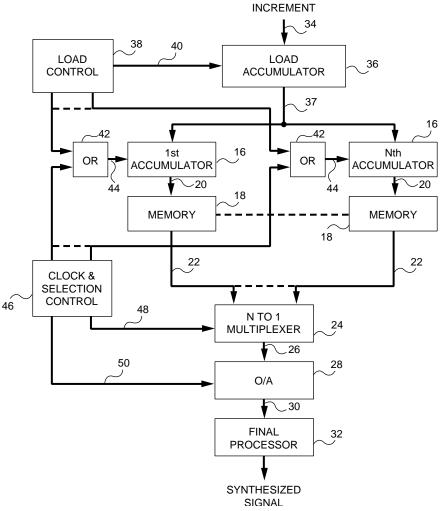

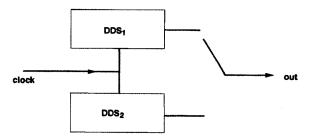

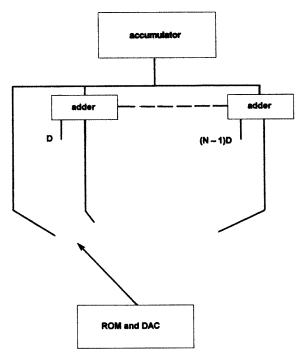

| 4-9-1 Very High-Speed Direct Digital Synthesizer                 | 128        |

| 4-9-2 Medium-Speed Direct Digital Synthesizer                    | 129        |

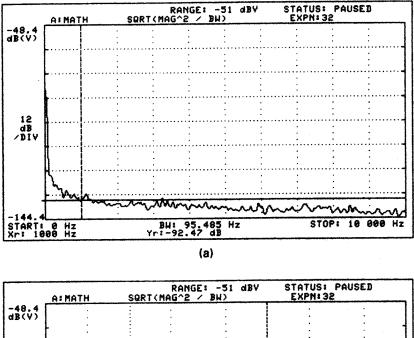

| 4-10 Performance Evaluation                                      | 133<br>133 |

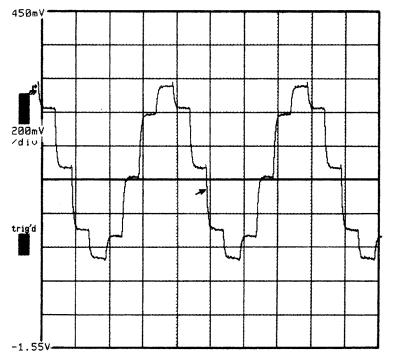

| 4-10-1 Switching Speed<br>4-10-2 Phase Noise                     | 133        |

| 4-10-2 Flase Noise<br>4-10-3 Spurious Signals                    | 133        |

| 4-10-4 Phase Continuity                                          | 134        |

| 4-10-5 Resolution                                                | 134        |

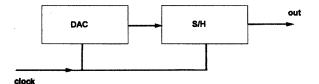

| 4-11 Sample-and-Hold Devices                                     | 134        |

| 4-12 Single-Bit DDS Revisited                                    | 135        |

| 4-13 Arbitrary Waveform Generators                               | 138        |

| 4-14 Digital Chirp DDS                                           | 140        |

| 4-15 Conclusion                                                  | 140        |

| Appendix 4A DDS Applications                                     | 141        |

| Appendix 4B DDS—Spectra and the Time Domain                      | 143        |

| Appendix 4C Sampling Theorem                                     | 157        |

| Appendix 4D The Effect of Phase Noise on Data Conversion Devices | 159        |

| References                                                       | 160        |

| Chapter 5. Phase-Locked Loop Synthesizers                           | 163        |

|---------------------------------------------------------------------|------------|

| 5-1 Main Components of PLL Synthesis                                | 164        |

| 5-1-1 Voltage Controlled Oscillators                                | 165        |

| 5-1-2 Analog Phase Detector                                         | 168        |

| 5-1-3 Digital Phase Detector 1                                      | 172        |

| 5-1-4 Digital Phase Detector 2                                      | 175        |

| 5-1-5 Digital Phase Detector 3                                      | 176        |

| 5-1-6 Digital/Analog Phase Detector 4<br>5-1-7 Dividers             | 177        |

|                                                                     | 180        |

| 5-2 Performance Evaluation<br>5-2-1 Wireless PLL ASIC Configuration | 184<br>198 |

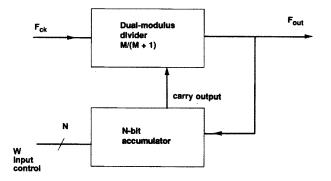

| 5-3 Fractional-N Synthesizers                                       | 201        |

| 5-3-1 Fractional-N Synthesis of the First Order                     | 201        |

| 5-3-2 Fractional- <i>N</i> Synthesis of the Second Order            | 216        |

| 5-4 Fractional- <i>N</i> Synthesis of the Third Order               | 220        |

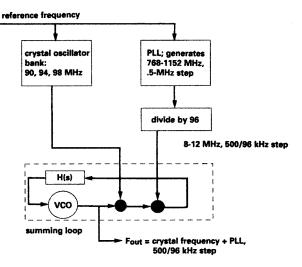

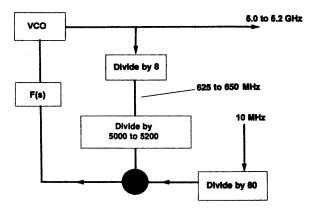

| 5-5 DDS-Based PLL                                                   | 224        |

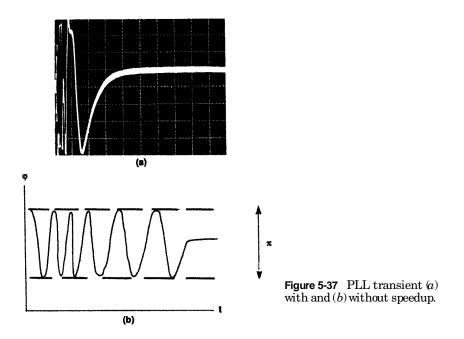

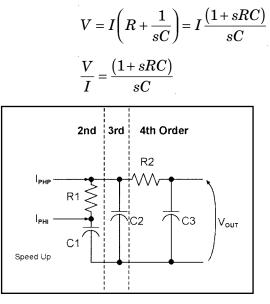

| 5-5-1 Speed Up                                                      | 226        |

| 5-6 Single-Chip PLL Synthesis                                       | 227        |

| 5-7 Conclusion                                                      | 230        |

| References                                                          | 235        |

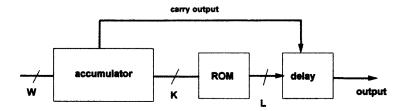

| Chapter 6. Accumulators                                             | 237        |

| 6-1 Binary Accumulators                                             | 237        |

| 6-2 Decimal Accumulators                                            | 245        |

| 6-3 Interface to ROM                                                | 246        |

| 6-4 Accumulator DDS                                                 | 248        |

| 6-5 Phase Adder and Accumulator Segmentation                        | 248        |

| 6-6 Conclusion                                                      | 250        |

| References                                                          | 250        |

| Chapter 7. Lookup Table and Sine ROM Compression                    | 251        |

| 7-1 ROM Algorithm                                                   | 252        |

| 7-2 Quadrant Compression                                            | 256        |

| 7-3 Compression Principles                                          | 259        |

| 7-4 Direct Taylor Approximation                                     | 260        |

| 7-5 Hutchison Algorithm                                             | 262        |

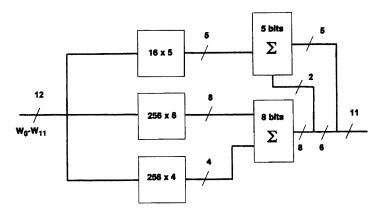

| 7-6 Sunderland Algorithm                                            | 266        |

| 7-7 Variations and Randomization                                    | 269        |

| 7-8 Auxiliary Function ROM Approximation                            | 271        |

| 7-8-1 Spurious Signal Analysis                                      | 274        |

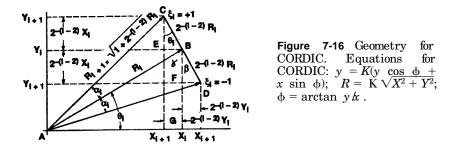

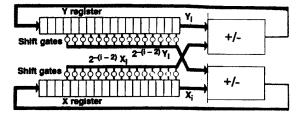

| 7-9 Coordinate Transformation (CORDIC)                              | 275        |

| 7-10 Other Methods                                                  | 278        |

| 7-11 Conclusion                                                     | 279        |

| References                                                          | 280        |

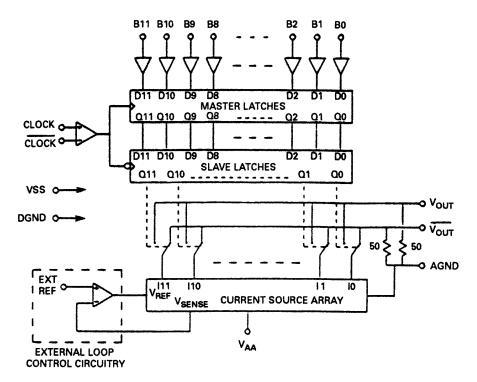

| Chapter 8. Digital-to-Analog Converters                 | 281        |

|---------------------------------------------------------|------------|

| 8-1 DAC Performance Evaluation                          | 282        |

| 8-2 DAC Principles of Operation                         | 285        |

| 8-3 DAC Parameters                                      | 292        |

| 8-3-1 Update Rate                                       | 292        |

| 8-3-2 Resolution                                        | 292        |

| 8-3-3 Logic Format                                      | 293        |

| 8-3-4 Setup-and-Hold Time                               | 293        |

| 8-3-5 Rise, Fall, and Settling Times                    | 293        |

| 8-3-6 Propagation Delay Time                            | 294        |

| 8-3-7 Differential Linearity                            | 294        |

| 8-3-8 Integral Nonlinearity                             | 294        |

| 8-3-9 Monotonicity                                      | 295        |

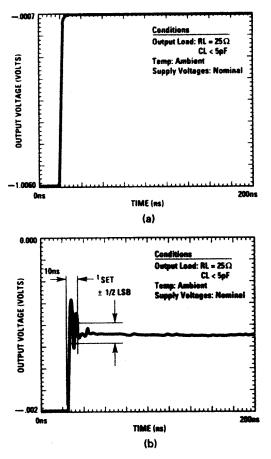

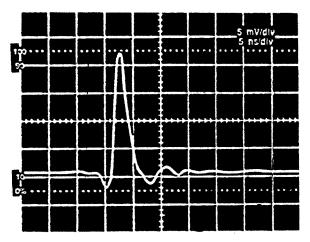

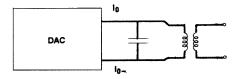

| 8-3-10 Multiplying Bandwidth<br>8-3-11 Glitch Energy    | 295<br>295 |

| 8-3-12 Symmetry                                         | 295        |

| 8-4 State-of-the-Art DACs                               |            |

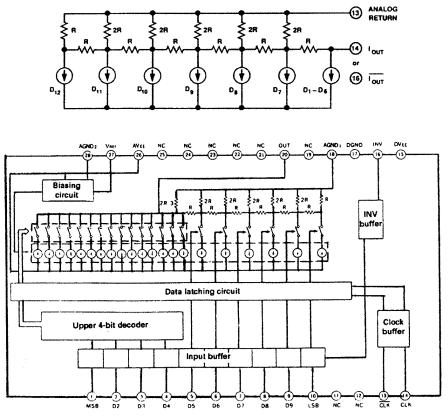

| 8-4 State-of-the-Art DACS<br>8-4-1 Low-Speed Operation  | 296<br>296 |

| 8-4-2 Medium-Speed Operation                            | 290        |

| 8-4-3 Very High-Speed Operation                         | 298        |

| 8-4-4 Other Recommended DACs                            | 299        |

| 8-5 Sine-Wave DAC                                       | 299        |

| 8-6 Multiplexing                                        | 299        |

| References                                              | 303        |

| References                                              | 303        |

| Chapter 9. Synthesizers in Use and Reference Generators | 305        |

| 9-1 Synthesizers in Use                                 | 305        |

| 9-1-1 Hewlett-Packard 3325B                             | 306        |

| 9-1-2 Hewlett-Packard 8662A                             | 307        |

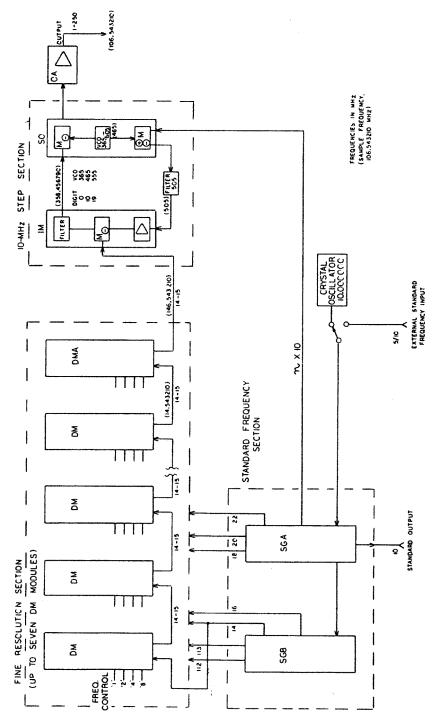

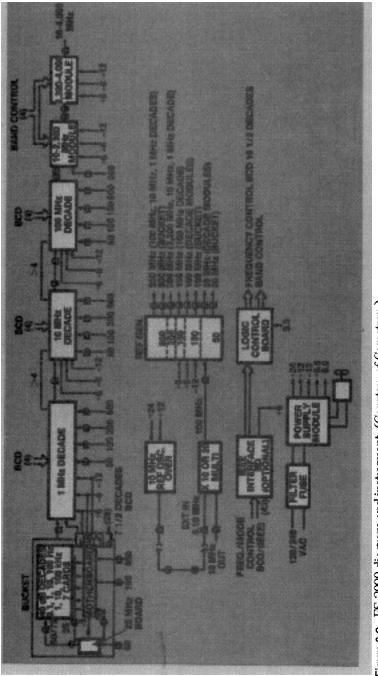

| 9-1-3 Program Test Sources 310                          | 307        |

| 9-1-4 Comstron/Aeroflex FS-2000                         | 309        |

| 9-1-5 Schomandl Models ND500 and ND1000                 | 309        |

| 9-1-6 Stanford Research DS345                           | 309        |

| 9-2 Reference Generators                                | 313        |

| 9-2-1 General Review                                    | 314        |

| 9-2-2 Crystal Oscillators                               | 316        |

| 9-3 Conclusion                                          | 319        |

| References                                              | 319        |

| Chapter 10. Original Paper and Software                 | 321        |

| 10-1 Tierney, Rader, and Gold Article                   | 321        |

| 10-2 Software Description                               | 322        |

Index 333

# ABOUT THIS BOOK AND CDROM

This book—the latest volume in our popular *Demystified* series of technical references—is an updated version of an earlier text, *Digital Techniques in Frequency Synthesis*, published by McGraw-Hill. In addition to the updated text, a CDROM has been added that contains an assortment of design tools, including an informative new reference in pdf format from Analog Devices called A *Technical Tutorial on Digital Signal Synthesis*. The CDROM also includes a fully searchable pdf file of the entire book contents. For a full list of the CDROM contents, see Chapter 10.

# ABOUT THE AUTHOR

Bar-Giora Goldberg received his education at the Technion-Israel Institute of Technology in Haifa, and he worked there for 10 years in communication and spread-spectrum systems. In 1984 he cofounded Sciteq Electronics, a world leader in the field of digital frequency synthesis, and he now heads Vitacomm, a company dedicated to frequency and time engineering products for wireless and high-speed telecommunications. Giora has written extensively, has been awarded several patents, and has been a major contributor to the introduction and development of DDS and fractional-N technologies. He is also associated with Besser Associates in the US and Continuous Education International (CEI) in Europe, companies dedicated to continuous education via seminars and on-line courses. This is a blank page.

# Preface

As in the first edition of this book, my purpose is to present to the designer a comprehensive review of digital techniques in modern frequency synthesis design. The text specifically addresses practical designers, and an attempt has been made to approach the subject heuristically, by using intuitive explanations and including many design examples.

Not long ago, frequency synthesis was considered a novelty. It was used in the more complex and demanding applications. Today, frequency synthesis is so ubiquitous that it is not even possible to say that its use is growing. Frequency synthesis is now so natural that every radio design uses only synthesized signals for generation and control. This is partly because the spectrum is so precious a commodity, and its use is controlled tightly by government and industry. Other reasons include the increase in complexity of modulation, the phenomenal increase in use, and the increase in convenience. No more dialing and fine-tuning; just push the button, and the channel is locked in with an accuracy that does not require correction.

Frequency synthesis therefore has entered the age where it is used in applications such as military radios, satellite communications terminals, and radars as well as in CB radios and hi-fi consumer electronics. It is not possible to consider the huge acceleration of cellular telephony and the still emerging markets of wireless and personal communications services (PCS) without the use of frequency synthesis.

Frequency synthesis is a fascinating technological discipline, as it includes both analog and digital technologies. To design a synthesizer one has to apply a great variety of disciplines such as oscillators, voltage-controlled oscillators, amplifiers, filters, phase detectors, logic, and low-noise dc amplification and filtering. This book, however, is not intended to be a general introduction to frequency synthesis; rather, it tries to focus on a segment of the technology.

There has obviously been a trend to "go digital" in the last 15 to 20 years. Although they are usually more complicated than analog, digital technologies offer excellent repeatability, much better accuracy, improved performance, and repeatability in production. This trend has not been ignored by frequency generation tech-There have been major advances in two nologies. kev technologies. The first is known as direct digital synthesis (DDS), a technology that generates the signal digitally and converts it via a digital-to-analog converter (DAC) to a sine wave. This technology is almost purely within what is known today as digital signal processing (DSP), but it has been in development for over 15 years within the domain of radio-frequency (RF) electronics engineering. The second is the digitalization of phase-locked loop (PLL) technology, the one that is the most popular and probably covers 98 percent of frequency synthesis and its evolution to what is referred to today as *fractional-N* synthesis.

Even very recent texts on PLL frequency synthesis have defined the technique as "generation of frequencies which are exact multiples of a reference." This definition is not accurate anymore. The more advanced synthesizers generate frequencies that are related to the reference but are not always exact multiples. In fact, the very principle of fractional-*N* PLL synthesis requires that the ratio of output frequency to the reference be a rational *fraction*. It so happens that these PLL technologies are also closely related to DDS and as such include DSP, a discipline that will find increased applicability in signal generation in the years to come.

This text was written mainly as a consequence of the rapid developments of these technologies and the lack of literature, especially the two subjects mentioned above. To the best of my knowledge, no other text exists that attempts to focus on the modernization and digitalization of signal generation.

Thus, the purpose of this book is to provide an introduction, training, and bibliographical material for designers. The text has been written specifically for designers, and many design examples have been included. Although the basics of each topic are covered, it is assumed that the reader has some understanding of frequency synthesis. There are many excellent general PLL books, and I have decided not to include too much of what has been already covered extensively before. Frequency synthesis, and especially the digital part of it, is now going through a major evolutionary period. Modern systems require high levels of integration, low power dissipation, and low cost. Digital technologies fit this bill precisely and allow the push in the technology. Frequency synthesis has received much attention from chip manufacturers, and a great variety of PLL and direct digital synthesizer chips have been available for several years. We are now seeing a major shift from the standard PLL to fractional-*N* PLL and a major increase in the use of DDS. These technologies are used in cellular and PCS applications as well as disk drives and satellite communications terminals. What can be more exciting and faster-moving than these markets today?

The collection of files on the accompanying CDROM has been provided to help the reader analyze and manipulate methods described in the text. The software has been devised for IBM PC compatibles, but it will also be applicable for Macs.

I would like to take this opportunity to thank former and current colleagues who contributed to this book while working with me or discussing various aspects of the technical details. No one can do it alone. A text like this presents a set of ideas and techniques that evolved through the ages, and personally through many years of practice. It is therefore not possible to mention all the people who made a contribution to the maturization of the technology of accurate timekeeping, but I am indebted to them.

I would like to extend my thanks to my friends and family, especially Pnina, who encouraged and supported this very long, hard effort. I would like to specifically thank my Technion mentors, Dr. Jacob Ziv and Israel Bar-David; and Henry Eisenson, a great friend, a brother, and a partner who always helps by giving support and encouragement.

Bar-Giora Goldberg

This is a blank page.

# Symbols

| a                             | angle                                                  |

|-------------------------------|--------------------------------------------------------|

| AM                            | amplitude modulation                                   |

| b                             | angle                                                  |

| с                             | angle                                                  |

| CORDIC                        | coordinate transformation                              |

| DAC                           | digital-to-analog converter                            |

| dB                            | decibel                                                |

| dBC                           | dB referred to carrier                                 |

| dBm                           | dB over 1 mW                                           |

| DDFS                          | direct digital frequency synthesizer                   |

| DDS                           | direct digital synthesis                               |

| Er, er                        | error                                                  |

| $f_i$                         | input frequency                                        |

| $f_m$                         | modulating frequency                                   |

| $F_{o}$                       | output frequency                                       |

| $F_{r}, F_{ref}$              | reference frequency                                    |

| $\mathbf{FM}$                 | frequency modulation                                   |

| $F_s$                         | sampling frequency                                     |

| gcd(a, b)                     | greatest common divisor                                |

| H(x)                          | transfer function                                      |

| int(x)                        | integer of x                                           |

| IF                            | intermediate frequency                                 |

| $K_{\rm d}$                   | phase detector gain constant                           |

| $K_0$                         | VCO gain constant                                      |

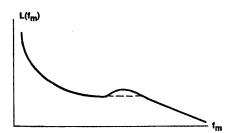

| $L_{\rm m}\left(f_{m}\right)$ | SSB noise density at $f_m$ from the carrier, in dBC/Hz |

| LFM                           | linear FM                                              |

| LSB                           | least significant bit                                  |

| m                             | index of modulation                                    |

|                               |                                                        |

| most significant bit                |

|-------------------------------------|

| numerical control oscillator        |

| phase modulation                    |

| radio frequency                     |

| sum (usually at accumulator output) |

| single sideband                     |

| sample time                         |

| voltage-controlled oscillator       |

| angle                               |

| angle                               |

| damping factor                      |

| phase                               |

| radial frequency                    |

| natural frequency                   |

| center frequency                    |

|                                     |

### Chapter

# 1

# Introduction to Frequency Synthesis

#### 1-1 Introduction and Definitions

This text deals with emerging modern digital techniques used to generate and modulate sine waves. These waveforms are used in almost all radio applications, communications, radar, digital communications, electronic imaging, and more. Such techniques either build the waveform from the "ground up" digitally (i.e., generate all the signal parameters such as phase, frequency, and amplitude digitally) and deal with the very fundamental nature of the waveform and its features (direct digital synthesis) or are part of the digital heart of modern phase-locked loop (PLL) synthesizers. This might seem, and is indeed, a common and known subject. Sine waves are truly natural waveforms and trigonometric functions that are well known and have been researched for a long time. Furthermore, frequency synthesis is quite a mature technology with extensive literature and comprehensive coverage in the professional meetings. Why another text on the subject? What is new besides application-specific integrated circuit (ASIC) technologies and silicon densities, geometry, and integration?

While the above statements are true, there is a continuous evolution in the technology. The generation of accurate waveforms plays a crucial role in almost all electronic equipment, from radar to home entertainment equipment, so the importance of the subject is clear. Clearly, the most important reason for the utilization of the now extremely popular PLL synthesizers in consumer electronics and other very popular applications at extremely low cost (and the popularization of frequency synthesis from consumer products all the way to complex requirements) is the advance of digital technology; integrated, high densities; and low-cost silicon single-PLL chips and ASICs. However, parallel to the advance of traditional PLL synthesis, there emerged other synthesis techniques, mainly digital in nature, *direct digital synthesis* (*DDS*) and fractional-*N* PLL synthesis. Thus, the classical PLL synthesizer is now being supplemented with a sizable element of digital technology and *digital signal processing* (*DSP*). Indeed the application of DSP techniques to frequency synthesis is still at an early stage.

The generation of sine waves by using digital methodologies requires generating the waveform from the ground up. This is fundamentally different from the PLL synthesizer, where the signal is available from an oscillator. It goes back to the very basic structure of the waveform itself and deals with its very basic characteristics rather than manipulates signals that have already been generated by an oscillator. Surprisingly, some of these very basic mathematical issues are being resolved only lately.

Unfortunately, in these specific fields, there is a lack of complete understanding of the mathematics as well as the standard implementation of working hardware. The operation of a direct digital synthesizer is far from intuitive, and its artifacts are sometimes alien to our (conservative or standard) thinking. Indeed, in this ongoing research effort, we have tried to recruit some very skilled professional mathematicians in the search for (1) effective sine *read-only memory* (*ROM*) (the transformation of  $\varphi$  to sin  $\varphi$ ) compression algorithms (indeed, the same old trigonometric functions; see Chap. 7), (2) a "minimal" amount of data necessary to represent the waveform, such as to meet a specific level of accuracy, and (3) a general formulation for the performance of DDS. We have not had much luck or enthusiasm.

We understand that this might not be the most exciting topic for mathematicians, but it has tremendous importance for electronics, radio, and radar designers. The challenge has to be met within the electronics community, and we have attempted to present a comprehensive introduction.

Although there are many excellent books on PLL synthesis (see References), mostly published in the 1980s, note that this is the

first attempt to write a comprehensive text on the subject of digital frequency synthesis, direct digital synthesis, and digital and fractional-*N* synthesis; and the number of sources is not overwhelming in this newly emerging technological discipline. We have found a paucity of literature in the field; and even though many articles have begun to appear in the last few years and the technology attracts much attention in professional meetings, comprehensive texts and bibliographies are needed. This is what this text attempts to supply. Every attempt is made to present a very comprehensive, updated bibliography.

Because of the paucity of literature, in this text we attempt to present an intuitive approach supplemented by many examples, in the hope that this book fills a current need as expressed to us by many young and beginning designers as well as others who are not familiar with the details and lack an intuitive understanding.

In this text, a *frequency synthesizer* is defined as a system that generates one or many frequencies derived from a single time base (frequency reference), in such a way that the ratio of the output to the reference frequency is a rational fraction. The frequency synthesizer output frequency preserves the long-term frequency stability (the accuracy) of the reference and operates as a device whose function is to generate frequencies that are multiples of the reference frequency (multiples by a single or many numbers). These multiples may be whole or fractions; but since only linear operations are used (in the frequency domain), these numbers can only be rational. A frequency synthesizer, as defined here, can thus generate an output frequency of, say, X/Y (where X and Y are whole numbers) times the reference frequency ( $\pi$  is not a rational number).

Three main, conventional techniques are being used currently for sine-wave synthesizers and are common throughout the industry. The most common and most popular technique uses the phase-locked loop synthesis. PLL synthesizers can be found in the most sophisticated radar systems or the most demanding satellite communications terminals as well as in car radios and stereo systems for home entertainment. The PLL is a feedback mechanism locking its output frequency to a reference. PLL synthesizers gained popularity for their simplicity and economics. Another synthesizer technique is known as *direct analog* (DA) frequency synthesis. In this technique, a group of reference frequencies is derived from the main reference; and these frequencies are mixed and filtered, added, subtracted, or divided according to the required output. However, there are no feedback mechanisms in the basic technique.

The DA frequency synthesis technique offers excellent spectral purity, especially close to the carrier, and excellent switching speed, which is a critical parameter in many designs and determines how fast the synthesizer can hop from one frequency to another.

The DA technique is usually much more complicated than PLL to execute and is therefore more expensive. DA synthesizers found applications in medical imaging and spectrometers, fast-switching antijam communications and radar, *electronic warfare (EW)* simulation, *automatic test equipment (ATE), radar cross-section (RCS)* measurement, and such uses where the advantages of the DA technique are a must at a premium cost.

The third technique, which is the focus of this book, is direct digital synthesis (DDS), which is a digital signal processing (DSP) discipline and uses digital circuitry and techniques to create, manipulate, and modulate a signal, digitally, and eventually convert the digital signal to its analog form by using a *digital-to-analog converter* (*DAC*).

Although the direct digital synthesizer [sometimes referred to as *numerically controlled oscillator* (*NCO*)] was invented almost 30 years ago (see Ref. 9 and Chap. 10), it started to attract attention only in the last 10 to 12 years. Due to the enormous evolution of digital technology and its tools, the technique evolved remarkably into an economical, high-performance tool and is now a major frequency synthesis method used by almost all synthesizer designers from instrument makers to applications like satellite communications, radar, medical imaging, and cellular telephony and amateur radios (most of which are anything but amateur).

Direct digital synthesizers offer fast switching speed, high resolution (the step size of the synthesizer), small size and low power, good economics, and the reliability and producibility of digital designs. In addition, since the signal is manipulated digitally, it is easy to modulate and achieve accuracies not attained by analog techniques and to conveniently interface with the computing machines that usually control the synthesizer. Another focal point of this text is the description of fractional-*N* PLL synthesis. This technique resembles DDS in almost all aspects and operates as a DDS "inside" the PLL architecture. Please note that in many designs, more than one synthesis technique is being utilized, and the designer "hybridizes" the design so that the advantage is taken of each technique being used and its weaknesses are suppressed. So it is quite common (and applications can be expected to grow) to see combinations of PLL and DDS or DA and DDS, and from time to time all three techniques are used in one design. Thus the basic three techniques indeed complement one another and enable the up-to-date competent designer to use all as needed to optimize the design as the applications and demands increase with the system complexity.

This text has 10 chapters. Chapter 1 is a general introduction and short description of frequency synthesis techniques, Chap. 2 deals with synthesizer system analysis, and Chap. 3 addresses measurement techniques pertinent to frequency synthesis. Chapter 4 details a variety of DDS technologies and deals with the quantization effects, their artifacts, and representations in DDS. Chapter 5 discusses PLL principles and the details of fractional-*N* PLL synthesis of various complexities. Chapters 6, 7, and 8 deal in detail with the cardinal components of DDS, namely, accumulators of binary and *binary-coded decimal (BCD)* structure, ROM lookup tables and ROM compression algorithms, and digital-toanalog converters. Chapter 9 gives a short review of state-of-theart reference oscillators and what we consider some remarkable instruments or products on the market that are directly related to digital frequency generation.

Chapter 10 is special, as it refers to a reprint of the original 1971 article by Tierney, Rader, and Gold that kicked off the DDS industry (Ref. 8), including some footnotes. This article is special not only because of its pioneering nature but also for the fact that it deals with all the cardinal issues of the subject. The chapter also includes a description of the programs contained on the accompanying CDROM.

#### 1-2 Synthesizer Parameters

Like any other engineering product, a *frequency synthesizer*(FS) needs to meet a set of specifications. In the following, a list of the

most common specifications is provided followed by a definition and industry standard conventions. Obviously, for different applications, different specifications are more important than others, and it is up to the designer to design for efficiency and economy. While a FS for a car radio needs to be moderately accurate, extremely reliable, very small and simple, and very inexpensive, a FS used in *magnetic resonance imaging*(MRI) must be very accurate, must have very high spectral purity, must be able to hop from frequency to frequency very quickly, and needs different modulation capabilities. While consumer electronic products need to operate in extreme environmental conditions (one expects the car radio to operate when powered up in extreme heat or cold conditions, and the vibrations of the cars are severe), the MRI spectrometer operates in a laboratory-controlled environment with little temperature variation and almost no shock or mechanical vibrations.

Designers are therefore required to compare their specifications to the best economical and practical solution. The specifications are divided into two groups: those that are related to the topics of this book and others that are more general and are beyond our scope. All the following sections pertain to generic specifications.

### 1-2-1 Frequency range

This specifies the output frequency range, including the lower and higher frequencies that can be obtained from the FS. The units of frequency are hertz (Hz), or cycles per second.

# 1-2-2 Frequency resolution

This parameter is also referred to as the *step size*, and it specifies the minimum step size of the frequency increments. So if a FS covers 10 to 100 MHz and has a step size of 10 Hz, it is capable of generating any frequency between 10 and 100 MHz in 10-Hz steps. Some manufacturers do not generate the last frequency, and so the same specification mentioned above will generate 10.0000 to 99.99999 MHz but not 100 MHz. In many applications, the step size is not fixed. This happens when a part of the synthesizer is generated by dividing a fixed frequency by a range of numbers.

#### 1-2-3 Output level

The output power level is usually expressed in decibels (0 dBm is 1 mW). The output power can either be fixed, say, +10 dBm, or can cover a range, say, -120 to +15 dBm. This specification will also include the output power resolution, for example, 1 dB or 0.1 dB.

### 1-2-4 Control and interface

This parameter specifies the control methodology and the interface to the FS. The control can be binary-coded decimal (BCD) or binary; it can be parallel or via a bus (usually an 8-bit bus) or serial; it can be transparent or latched. When the control is latched, there is a register that receives the control word and upon activation (by a latch command) loads the control word into the FS (also referred to as *double buffering*). Some FSs use positive logic and others use negative; and in many general-purpose instruments, GPIB or IEEE-488 is currently the standard interface. VXI is an emerging new interface standard for instrumentation.

Most single-chip synthesizers, especially PLL, make extensive use of the serial interface to allow small packages and highly integrated functionality.

### 1-2-5 Output flatness

This parameter specifies the flatness of the output power and is measured in decibels (dB). For example, the output power is specified as 10 dBm  $\pm 1$  dB, where dBm means decibels over 1 milliwatt (mW).

### 1-2-6 Output impedance

This parameter specifies the nominal output impedance of the FS and usually is also the recommended load impedance. In most radio-frequency and microwave equipment, this is 50 ohms ( $\Omega$ ). In video it is usually 75  $\Omega$  and in audio equipment 600  $\Omega$ .

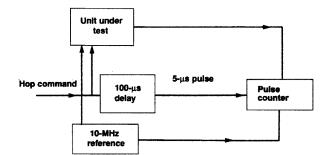

### 1-2-7 Switching speed

This parameter specifies the speed at which the FS can hop from frequency to frequency. There are many definitions for this parameter. In some applications the requirement is to settle to within a specific frequency ( $\pm x$  Hz) from the desired new frequency (say, 50 Hz or 5 kHz from the desired frequency). Suppose that the specification is to cover 10 to 100 MHz and switch to within 1 kHz in less than 100 microseconds ( $\mu$ s). To measure this parameter, a counter is set to measure the new frequency (say the FS is commanded to hop between 10 and 100 MHz periodically) and is timed to start measuring only 100  $\mu$ s after the command bit is activated (say, for 5  $\mu$ s, because the time allowed must be short relative to the specification time). If the measurement is either 10 or 100 MHz (depending on where we command the counter to measure) within  $\pm$  1 kHz, then the specification has been met. Obviously in such a measurement a pulsed counter must be used, and its gating time must be specified, too.

A more common and more demanding specification defines the switching speed by the time it takes the output phase to settle to 0.1 rad of the final phase.

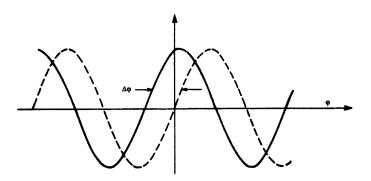

If the FS generates  $A \cos(\omega_1 t + \varphi_1)$  and is controlled to a new frequency, say,  $A \cos(\omega_2 t + \varphi_2)$ , the signal phase will go through a transient from  $\omega_1 t + \varphi_1$  to  $\omega_2 t + \varphi_2$  and eventually will settle at  $\omega_2 t + \varphi_2$ . The standard definition of *switching speed* is the time it takes the switching transient to achieve an output phase of  $\omega_2 t + \varphi_2 \pm 0.1$  rad (approximately 5.7°). Note that in most cases  $\varphi_1$  and  $\varphi_2$  are not a part of the measurement since their values are not a parameter in the overall system and the user does not care about their values. But from time to time stringent requirements arise where the phase is also specified relative to some given reference. See Chap. 2.

#### 1-2-8 Phase transient

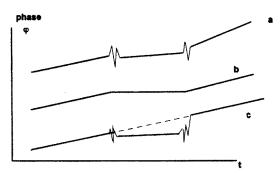

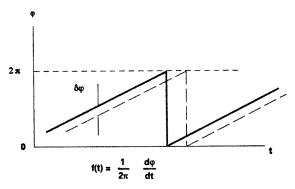

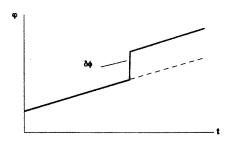

In most applications, the behavior of the phase when in a transient state is not defined, as shown in part a of Fig. 1-1. However, many applications need to define the transient characteristics very carefully. Two typical requirements are as follows:

**1-2-8-1 Phase-continuous switching.** This means that during switching the phase transition shall exhibit (almost) no transient and shall ideally look as shown in part b of Fig. 1-1. Such a feature

Figure 1-1 Phase switching in transition.

is important when one is attempting to generate a synthesized sweep, also known as *linear FM*, and has many applications in measurements, EW, radar, and specific modulations [e.g., *mini* - *mum shift keying* (MSK)]. Such a phase transient is smooth and generates very little "noise," and this is very desirable in systems and networks.

**1-2-8-2 Phase memory switching.** This means that if the FS runs at  $f_1$  and then is switched to  $f_2$ ,  $f_3$ ,  $f_4$ , ... and back to  $f_1$ , then it will resume the phase where it would have been if it were running continuously at  $f_1$ , as shown in part *c* of Fig. 1-1.

This requirement is simple to achieve if all the output frequencies are generated simultaneously and are switched to the specific output  $(f_1, f_2, f_3, ...)$  upon command. In such a case, every generator will continue to oscillate even when it is not used, and therefore, when it is reconnected, it will preserve its phase. However, if a single switched output is used, this requirement is sometimes quite tricky to achieve (see Ref. 12). Many applications require such a feature, e.g., coherent pulse Doppler radar imagers that frequency-hop but use coherent pulse detection (for predetection integration).

#### 1-2-9 Harmonics

This parameter specifies the level of harmonics of the output frequency and depends on many components inside the FS. It is expressed in decibels relative to the output frequency (carrier) output power.

#### 1-2-10 Spurious output

This specification defines the level of any discrete output frequency spectral line not related to the carrier. Most users do not consider harmonics as spurious signals. However, subharmonics, because of either multiplications or those that appear as DDS artifacts, are considered spurious signals even though they are sometimes specified separately. This parameter is expressed in decibels relative to the carrier output power. Unlike noise, spurious signals are only discrete spectral lines not related to the carrier, meaning that they exhibit periodicity.

#### 1-2-11 Phase noise

From the purist's standpoint, there are no deterministic signals in the real world! All real signals are narrow-band noise. Every signal we generate is derived from an oscillator. Oscillators are positive feedback amplifiers with a resonance circuit in their feedback path. Since noise always exists in the circuit, upon power up this noise is amplified in the resonator band until a level of saturation is achieved. Then the oscillator passes from the transient to its steady state. Thus, the quality of the signal is mainly determined by the resonator Q. The signal that we usually refer to as a "sine wave" is actually *narrow-band noise*. The quality of the signal is determined by how much of its energy is contained close to the carrier. The center frequency is actually the average-the mean-of the noise frequency. Phase noise in a way is the standard deviation of the noise. In very high-quality signals, like crystal oscillators (Q range of 20,000–200,000), 99.99% of the signal energy can be contained within .1 Hz of the center frequency.

This parameter specifies the phase noise of the output carrier relative to an "ideal" output. The ideal output of a sine-wave generator is given by

$$A\sin\left(\omega_0 t + \varphi\right) \tag{1-1}$$

and its presentation in the frequency domain is a delta (Dirac) function at angular frequency  $\omega_0$ :

$$F(\omega) = A \qquad (\omega - \omega_0) \tag{1-2}$$

Such a signal contains all its energy in a single frequency  $\omega_0$  and

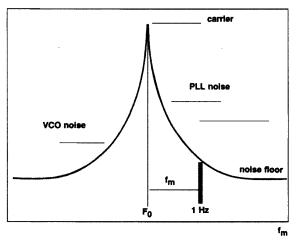

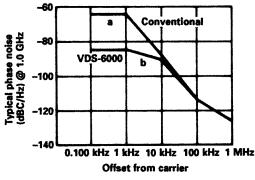

Figure 1-2 Typical phase noise plot.

has an ideal bandwidth of zero. Such a signal must be of infinite time (otherwise its spectrum will have a finite width greater than zero) and infinite power. However, the reference to a delta function is convenient for theoretical evaluations. High-quality frequency synthesizers generate signals which contain 99.99 percent of their energy in less than 1 Hz of bandwidth around the carrier. Crystal oscillators can contain 99.99 percent of their energy in less than 0.01-Hz bandwidth.

Obviously, in the real world the only signals we can generate are given by

$$A[1 + n_1(t)]\sin[\omega_0 t + n_2(t) + \varphi]$$

(1-3)

where  $n_1(t)$  represents the amplitude instability and  $n_2(t)$  represents the phase perturbations, both relative to the ideal case. These noise functions are random by nature and represent a spectrum that has to be designed to meet a specification.

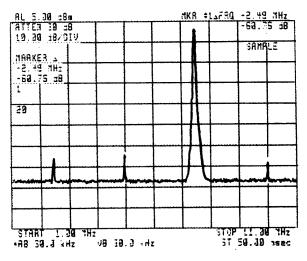

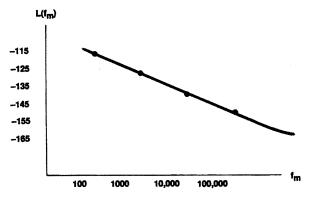

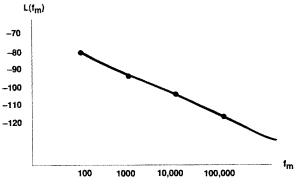

In most synthesizers the amplitude noise is much lower than the phase noise and is not specified separately. However, the phase noise is a major parameter and is expressed in a few ways. The most common way is to specify the noise density in 1-Hz bandwidth at specific offset  $f_m$  from the carrier, as shown in Fig. 1-2. For the ideal signal, there is no energy at any offset from the carrier. Although this has become a de facto industry standard in defining and specifying phase noise, the measurement itself is sometimes

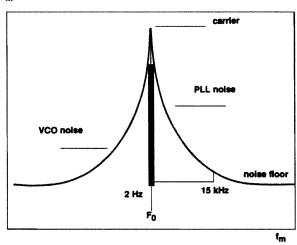

Figure 1-3 Integrated phase noise. S/N = signal/noise in 30 kHz (excluding 2 Hz around the carrier).

quite complicated, and the instruments necessary to make the measurement are quite expensive.

Another method of defining phase noise is to measure the integrated noise in a given bandwidth around the carrier but excluding  $\pm 1$  Hz around the carrier. This is shown in Fig. 1-3. Obviously this method is related to the first one by the integration of the noise energy under the phase noise curve. However, compared to phase noise measurement, this is a simple measurement to make. The information available from such a measurement is a good indicator of the overall performance of the unit; but since this is an integrating measurement, the total noise power is measured even though its detailed spectral shape is lost. Traditionally (probably because of applications related to voice), the noise bandwidth is measured between 1 Hz and 15 kHz. So the measurement is the ratio of the total signal power to its noise from 1 to 15 kHz from the carrier (30 kHz of noise bandwidth). As an indicator, high-quality VHF/UHF synthesizers achieve a ratio of 60 to 70 dB and better.

Another method is to measure either FM noise, given in hertz root mean square or phase noise in degrees root mean square. Yet another method is to measure the phase noise in the time domain, and it is referred to as the *Alan variance*. By measuring the time

fluctuations it is possible to infer the spectrum of the signal. All these methods are related mathematically and must be consistent with one another. For detailed analysis of phase noise, see Chap. 2 and Refs. 13 and 14. Usually the FS phase noise reaches a noise floor, as shown in Fig. 1-2, and this parameter is sometimes specified, too. [A program to convert  $L(f_m)$  to root-mean-square degrees is included on a disk the reader may obtain from the author (see Chap. 10).]

### 1-2-12 Standard reference

Since all synthesizers use a reference time base input, this specifies the reference frequency (usually 5 or 10 MHz, but there are many others), and its parameters such as stability, phase noise, spurious signals, and power level.

# 1-3 Auxiliary Specifications

These specifications are usually related to the execution of the specific synthesizer but are not dealt with here. Usually they include parameters such as size, power supply requirements, environmental factors, quality, and reliability.

# 1-4 Review of Synthesis Techniques

In this section we present a concise review of the three major synthesis techniques. But before we go into the details of these main techniques, it is worthwhile to mention what might be the simplest and crudest technique—digital frequency synthesis, namely, a programmable divider. This is not a common way of synthesizing frequencies, but it is applicable for a variety of programs. For example, a clock of 80 MHz and a divider in the range of 2000 to 4000 produce a synthesizer with 2000 frequencies, in the range of 20 to 40 kHz. The step size is not constant and actually varies (in this case) 4:1, but is 20 Hz maximum, which is good enough for many applications, especially in communications, that can make use of this simple device, which can be easily executed today by using CMOS gate array technology at extremely low power. This type of device is beyond the scope of this text.

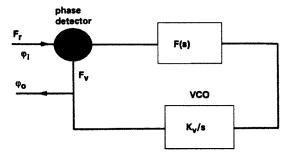

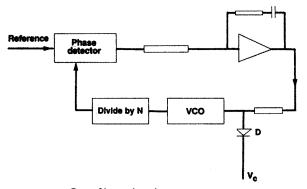

Figure 1-4 PLL block diagram.

Figure 1-5 VCO control characteristics and piecewise linearization.

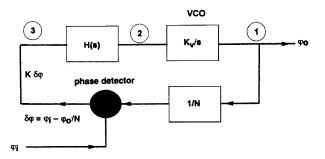

#### 1-4-1 Phase-locked loop

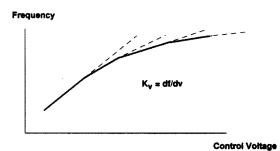

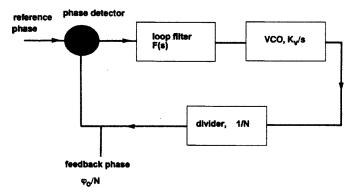

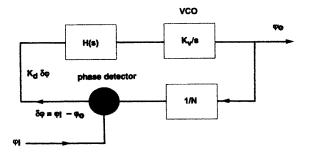

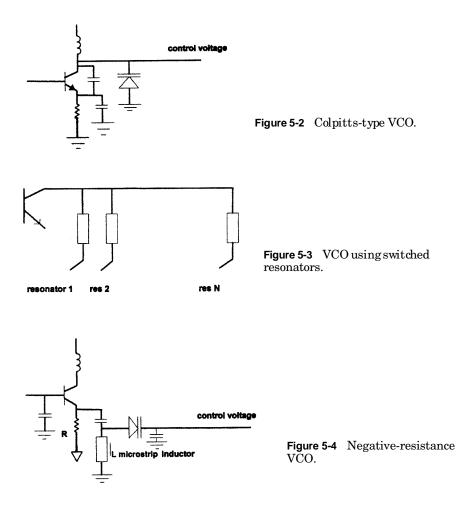

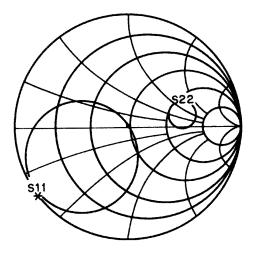

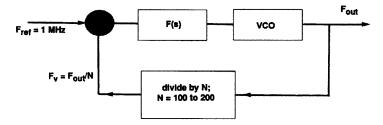

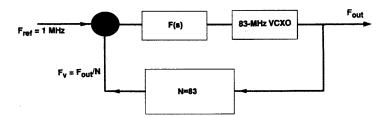

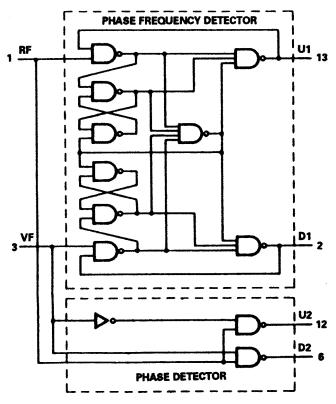

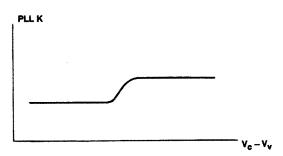

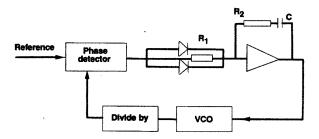

As mentioned before, the phase-locked loop (PLL) is by far the most popular frequency synthesis technique. It is basically a nonlinear (the phase detector is a nonlinear device) feedback loop, as shown in Fig. 1-4. The PLL consists of a voltage controlled oscillator (VCO), a phase detector, a variety of dividers, and a loop filter.

The VCO is a device whose output frequency depends on the input control voltage. The relation is nonlinear (a typical response is shown in Fig. 1-5) but monotonic. However, when locked, the VCO can be assumed to be linear; it is both practical and convenient for analytical purposes. Variation in the VCO control characteristics (i.e., this nonlinearity) affects the loop parameters, and loop linearization (or compensation) is used extensively. Generally, the VCO output waveform is given by

$$A_{\text{out}}[t, \omega(v)] = A(t, v) \sin[\omega(v)t + \varphi]$$

(1-4)

where *A* is the signal amplitude and  $\omega$  is the angular frequency, both depending on time *t*, and control voltage *v*.

As a first approximation, we assume that *A* has a constant envelope (does not depend on *t* or *v*) and that  $\omega$  is a linear function of *v*. Therefore we can write Eq. (1-4) as

$$A_{\text{out}}(t) = A \sin[(\omega_0 + K_v v)t + \varphi]$$

(1-5)

Here  $K_v$  is the VCO constant [rad/(V s)]. Since we assume that the frequency is linearly dependent on v and is given by

$$\omega(v) = \omega_0 + K_v v \tag{1-6}$$

as mentioned, the linearization is justified and is assumed for the purpose of simpler analysis. In reality, when the loop is locked, frequency variations are tiny, and the constant-VCO assumption is correct as a piecewise linearization of the graph in Fig. 1-5.

Since phase is the integral of the angular frequency, we can complete the approximation by writing that the VCO transfer function, given by

$$\frac{\varphi_o(s)}{V} = \frac{K_v}{s} \tag{1-7}$$

as the Laplace transfer function of the VCO output phase.

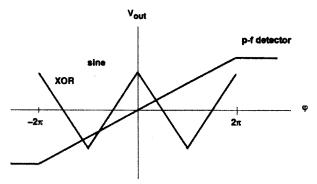

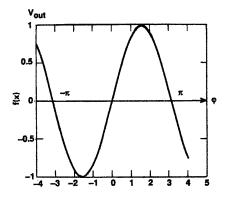

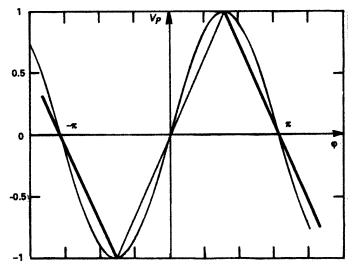

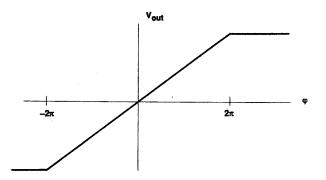

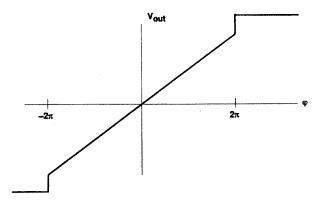

The phase detector produces an output voltage proportional to the difference in phase between its inputs and is always a nonlinear function. Typical phase detector output transfer functions are shown in Fig. 1-6. However, close to the locked position this func-

Figure 1-6 Phase detector output characteristics. p-f = phase-frequency.

tion can be assumed to be linear (this is also justified since in the locked condition most frequency synthesizers operate with a very high signal-to-noise ratio and the phase detector therefore operates mainly at a fixed-phase position). Hence

$$V_d = K_d(\varphi_i - \varphi_o) \qquad \text{V/rad} \tag{1-8}$$

where  $V_d$  is the phase detector output voltage.

Now the loop transfer functions can be described as

$$V_d = K_d[\varphi_i(s) - \varphi_o(s)] \tag{1-9}$$

Let

$$V_c(s) = V_d(s)F(s)$$

control voltage (1-10)

where F(s) is the loop filter transfer function and  $V_c$  is the VCO control voltage. Solving these simple equations yields

$$\varphi_o(s) = \frac{\varphi_i(s)K_dK_vF(s)}{s + K_vK_dF(s)}$$

(1-11)

and the transfer function  $H(s) = \varphi_o(s)/\varphi_i(s)$  is given by

$$H(s) = \frac{K_d K_v F(s)}{s + K_d K_v F(s)}$$

(1-12)

Also, following these equations will show that the *error transfer function*, defined as

$$H_e(s) = \frac{\varphi_i(s) - \varphi_o(s)}{\varphi_i(s)}$$

(1-13)

is given by

$$H_e(s) = \frac{s}{s + K_d K_v F(s)}$$

(1-14)

Since we linearized all components, given  $K_v$  and  $K_d$ , the feedback loop behavior depends mainly on F(s).

Also note that the error function has high-pass characteristics, and therefore a true direct-current (dc) modulation of a PLL circuit is not possible. This function, however, also referred to as *dc frequency modulation*, is possible in other synthesis techniques. **1-4-1-1** First-order loop. A first-order loop is obtained when F(s) = constant, say, *A*. This means that the loop filter has a fixed gain but no dependence on frequency. The gain is necessary because of the difference between the output voltage of the phase detector and the required control voltage input to the VCO. (Most phase detectors produce output voltage levels of 0 to 2 or 5 V while the VCO control might require 10, 15, and sometimes 24 or even 50 V to cover its operating range.)

In this case, the loop transfer function  $\varphi_{0}(s)/\varphi_{i}(s) = H(s)$  reduces to

$$H(s) = \frac{K_v K_d A}{s + K_v K_d A}$$

(1-15)

For convenience we shall designate

$$K = K_v K_d A \tag{1-16}$$

and rewrite H(s) for a first-order loop:

$$H(s) = \frac{K}{s+K} \tag{1-17}$$

As can be seen, this loop leaves few options to the designer since the loop parameters  $K_v$ ,  $K_d$ , and A dictate the behavior of the feedback mechanism. Note that there is only one integrator in this PLL (phase is the integral of frequency, and the VCO characteristics in the Laplace domain have been described as  $K_v/s$ ) and therefore only one pole in the transfer function. An intuitive approach to the loop behavior can be taken by realizing that the transfer function is that of a single-pole low-pass (*RC*) filter. So, for a step in the input phase, say  $\varphi_v$ , the output phase will be given by

$$\varphi_{o}(t) = \varphi_{i}(1 - e^{-t/K})$$

(1-18)

and the phase error will be given by

$$\varphi_o - \varphi_i = \varphi_i e^{-t/K} \tag{1-19}$$

This assumes that the input phase step is fixed. This shows immediately that in such a loop, fixing  $K_v$ ,  $K_d$ , and A determines immediately the dynamics of the loop and its noise *bandwidth* (*BW*), which is defined by

$$BW = \int_0 |H(j\omega)|^2 df \qquad (1-20)$$

and is given by K/4.

The noise BW of a PLL is an indicator of the loop bandwidth, and its calculation presents the integrated bandwidth of the loop and a measure of its speed of response.

The transfer function of a first-order loop is similar to that of an RC filter; and the error transfer function e(s), indicating the error after a transient has settled,  $e(s) = H_e(s)\varphi_i(s)$ , is given by

$$e(s) = rac{s \varphi_i(s)}{s + K} \qquad rac{e(s)}{\varphi_i(s)} = rac{s}{s + K}$$

(1-21)

The error function can be calculated for a phase step by using the final-value theorem, which states that steady state in the time domain can be calculated from the transfer function in the frequency domain. Accordingly, for a phase step  $\varphi_i$ , the final value of the error is given by

$$\int_{-\infty}^{+} x(t) = \lim_{s = 0} sX(s)$$

(1-22)

where X(s) is the Laplace transform of x(t) and is therefore in this case

$$\lim_{s=0} \frac{s\varphi_i}{s+K} = 0 \tag{1-23}$$

Thus a phase shift in the input will be tracked by the output. However, a phase ramp, or a frequency error  $d\omega$ , yields

$$\lim_{s=0} \frac{d\omega}{s+K} = \frac{d\omega}{K}$$

(1-24)

Thus a first-order loop when one is tracking a phase ramp (frequency change) will generate a fixed phase error, proportional to  $d\omega$  and K. Obviously higher-level changes in the phase rate (parabolic and higher) cannot be tracked and create a diverging error. With only one integrator (the VCO) in the loop, this is expected.

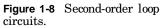

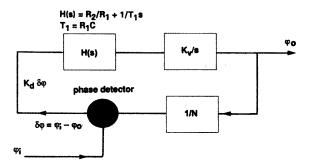

This PLL structure is not particularly popular for FSs because of its lack of degrees of freedom in the design. **1-4-1-2 Second-order loop.** This model of the PLL is the most commonly used in the FS industry. Although many designers claim that in reality there are no second-order loops (since the devices used to realize the loop filter always add poles), this represents an approximation to an analysis that is simple and yields a good theoretical approximation of the behavior of the majority of PLL designs. In this case

$$F(s) = \frac{1 + sT_2}{sT_1}$$

(1-25)

[note the added integrator in the network F(s)] and

$$H(s) = \frac{K(sT_2 + 1)/(T_1)}{s^2 + s(1 + KT_2)/(T_1) + K/(T_1)}$$

(1-26)

Following the common notions of control theory, we define

$$_{n} = \sqrt{\frac{K}{T_{1}}} \tag{1-27}$$

and

$$\xi = \frac{\omega_n T_2}{2} \tag{1-28}$$

and the transfer function can now be represented as

$$H(s) = \frac{2\xi\omega_n s + \omega_n^2}{s^2 + 2s\omega_n \xi + \omega_n^2}$$

(1-29)

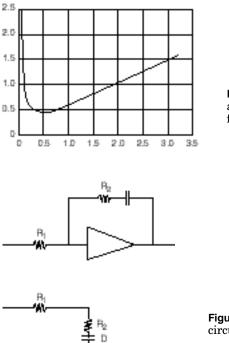

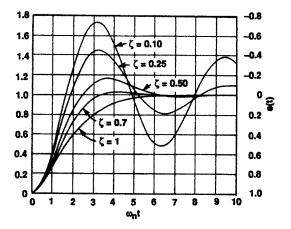

As in most second-order control systems, the characteristics are controlled by  $\omega_n$ , also called the *loop natural frequency*, and the damping factor  $\xi$  (both designators imported from control theory). Such a loop can be controlled by F(s) to arbitrary  $\xi$  and  $\omega_n$ , and it can be shown (Ref. 1) that the loop BW, as defined in Eq. (1-20), is given by

$$B_L = \frac{\omega_n}{2(\xi + 1/4\xi)}$$

(1-30)

as shown in Fig. 1-7.

The loop filter is usually realized by either a passive network or an active integrator, as shown in Fig. 1-8. The design equations for

**Figure 1-7** Loop bandwidth as a function of the damping factor.

the integrator network are given by

$$_{n} = \sqrt{\frac{K}{T_{1}}} \tag{1-31}$$

$$\xi = \frac{\omega_n T_2}{2} \tag{1-32}$$

and for the passive network by

$$_{n} = \sqrt{\frac{K}{T_{1} + T_{2}}}$$

(1-33)

$$\xi = \frac{\omega_n (T_2 + 1/K)}{2}$$

(1-34)

Figure 1-9 PLL for frequency synthesis.

Note that  $K_d$  is in volts per radian,  $K_v$  in rad/(s · V), K in 1/s, and  $\omega_n$  in radians per second;  $\xi$  is dimensionless.

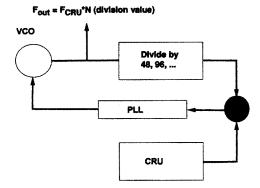

In PLL synthesizers, the output of the VCO is usually followed by a divider, as shown in Fig. 1-9. In the lock conditions, the output frequency will be given by  $NF_{ref}$ , and so by changing N, the output frequency is changed. All the equations stay the same, except the VCO constant changes from  $K_n$  to  $K_nN$ .

The transfer function is given by

$$H(s) = \frac{KF(s)}{s + KF(s)/N}$$

(1-35)

For a second-order loop, it can be shown that the steady-state error for a step input and for a linear phase ramp  $d\omega$  is 0 (there are two integrators in the loop), but a parabolic phase rate (linear FM) cannot be tracked and a frequency error is generated. Obviously higher-order loops are used for applications where higher-level phase changes are required, but the majority of PLL applications, especially for frequency synthesis, use second-order designs.

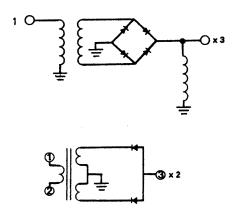

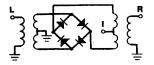

#### 1-4-2 Direct analog synthesis

Unlike PLL, the direct analog (DA) technique uses arithmetic operations in the frequency domain (but no closed-loop feedback mechanisms) to convert the input reference signal to the required output frequency. The main tools for the DA technique are therefore comb generators, multipliers, mix and filtering, and division.

16.00 to 16.99

Figure 1-10 Direct analog design using multiple references. BPF = bandpass filter.

Because such operations are complex, it is desirable to design repeating building blocks, so that their production will be economical; otherwise, price and complexity are both very high.

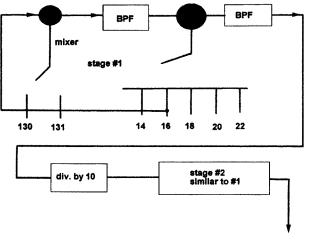

To demonstrate the basic elements of the DA technique, we consider a tentative design of a synthesizer that covers 16.0 to 16.99 MHz of output frequency range, has 0.01-MHz (10-kHz) step size, all derived from a 10-MHz reference. This demonstration design (Fig. 1-10) requires the following reference frequencies: 14, 16, 18, 20, 22, 130, and 131 MHz. Given these reference frequencies, the generation of which is not necessarily trivial, a common block might look like that in Fig. 1-10.

Note that the output of the first stage serves as the input to the second stage (similar), and so at the output of the first stage 10 frequencies will be generated, from 16.0 to 16.9 MHz, but at the output of the second, the complete range of 16.0 to 16.99 MHz is achieved (100 frequencies). Note that by adding more similar stages, the resolution of the synthesizer can be increased to any required level. The same stage can therefore be used repeatedly without the need to generate more references.

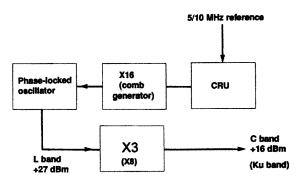

Usually, in such designs, the reference frequencies are generated by direct analog methods rather than PLL, i.e., comb generators, filters, mixing, and dividing. As an example, one possible

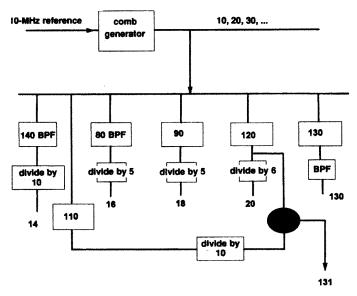

Figure 1-11 Reference generation for DA design.

method is demonstrated in Fig. 1-11. The 10-MHz comb generates 10-MHz comb lines 10, 20, 30, ..., 140 MHz. The 14 is generated by 140/10 (or 70/5), the 16 by 80/5, the 18 by 90/5, the 20 by 120/6, the 22 by 110/5, the 130 by 120 + 10 (both available), and the 131 by 120 (available) + 110 (available)/10.

This architecture usually operates in blocks of decades and is used here to demonstrate the DA principles. There can be many other variations, but this is quite a typical and efficient design. The basic element of DA is therefore mix and filter.

Note that the spectral purity depends on the spectral purity of the references (usually excellent), and the speed of the synthesizer in this case depends on the speed of the switches that switch in and out the reference frequencies and the response time of the filters.

The above design can achieve switching speeds of 3 to 10 microseconds ( $\mu$ s) depending on the detailed design.

Note also that if all the above operations were designed at frequencies 5 times higher, the filter's bandwidth would have increased 5 times and the speed would depend mainly on the speed of the switches. Such a design could achieve submicrosecond speed. Obviously the compromise will involve cost.

Note also that such a design does not possess the quality of phase memory, although at first it might look as if it does. Since all the references run continuously, they all maintain phase memory. The problem occurs in the divider. We know that mix and filter preserve the phase of the references since it is basically a *sin* - *gle-sideband* (*SSB*) operation that can be expressed as

$$e^{j(\omega_{1}t + \varphi_{1})} \cdot e^{j(\omega_{2}t + \varphi_{2})} = e^{j[(\omega_{1} + \omega_{2})t + \varphi_{1} + \varphi_{2})]}$$

(1-36)

and the phases are preserved. However, the divider (here by 10) will suffer a transient, and its output phase can be at any one of 10 possible output phase states, and so the phase preservation is lost. Therefore, there is no phase continuous switching in such a design, and this means that linear FM sweeps cannot be generated.

As a general rule for such block decade design, the output frequency is given by

$$F_{\text{out}} = F_i + \frac{F_1}{10} + \frac{F_2}{100} + \dots = F_i + \sum_{j=1}^n F_j(10^{-j}) \quad (1-37)$$

where  $F_i$  and  $F_i$  are the inputs to the block.

In the above case, if N = 0 were the last stage and did not contain the divide-by-10 device common to all other stages, then the output frequency range would be 160.0 to 169.99... and the number of 9s (or the resolution) depends on the number of stages being employed. This is convenient for two reasons: the frequency coverage is 10 MHz (rather than 1 MHz for the common block), and the final frequency is higher and easier to convert upward.

Early DA designs were quite complicated, had many crystal references in them, and had complex architectures. All this is gone now. All DA designs consist of repeatable blocks, which imply efficiency in production and elegance.

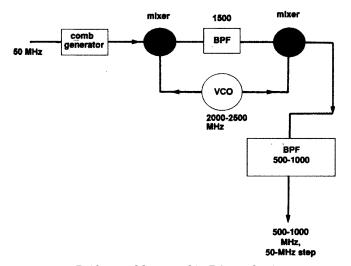

Another technique that is usually associated with DA is called *drift cancel* and is worth mentioning. The general idea is demonstrated in Fig. 1-12.

A comb generator is used to generate a comb spectra line, in this example 50 MHz apart, and a free-running VCO and a *bandpass filter* (*BPF*) are used to output only one line at a time.

In the example, the VCO will be tuned to 2000 MHz to output 500 MHz. If the VCO is tuned to 2050 MHz, the output will be 550 MHz; the VCO tuned to 2100 generates 400 MHz; and so on. Note that the mathematical operation here is

$$F_{\rm out} = F_{\rm VCO} - (F_{\rm VCO} - F_{\rm comb \ line}) = F_{\rm comb \ line} \qquad (1-38)$$

The VCO serves an auxiliary function and cancels itself. The VCO can be free-running since the level of accuracy necessary is only to bring the desired comb line into the BPF passband.

Although this is a simple, elegant, and economical technique, the design is usually more complicated than it shows. Excellent isolation must be maintained to eliminate leakage of undesired comb lines. In addition, the cancellation effect must be calculated relative to the phase noise of the free-running VCO. Ideally the two VCO paths should have the same delay, and the signals should cancel perfectly. In reality, this is not the case, and the cancellation effect is finite. It is usually very good close to the carrier, but degrades as we move away from the carrier. The reason is clear because the cancellation takes the form  $\varphi(t) - \varphi(t + T)$ , where *T* is the difference in the delay path of the two branches  $\varphi = \omega_0 t + n(t)$ . Thus the cancellation takes the form

$$\varphi_n = \omega_0 T + n(t) - n(t+T)$$

(1-39)

A typical cancellation profile for a 2.5-MHz BPF is given in Table 1-1. This implies the requirement of good phase noise characteristics from the VCO, since at, say, 100 kHz from the carrier, the cancellation effect will improve the VCO phase noise by only 15

Figure 1-12 Drift-cancel loop used in DA synthesizers.

| $(\text{Deray between cancentation paths is approximately 1 } \mu s)$ |                   |  |  |  |  |  |

|-----------------------------------------------------------------------|-------------------|--|--|--|--|--|

| Offset from carrier (Hz)                                              | Cancellation (dB) |  |  |  |  |  |

| $1	imes 10^3$                                                         | 45                |  |  |  |  |  |

| $1	imes 10^4$                                                         | 30                |  |  |  |  |  |

| $5	imes 10^4$                                                         | 20                |  |  |  |  |  |

| $1	imes 10^5$                                                         | 15                |  |  |  |  |  |

| $5	imes 10^5$                                                         | 5                 |  |  |  |  |  |

| $1	imes 10^6$                                                         | —                 |  |  |  |  |  |

#### TABLE 1-1 Typical Noise Cancellation of 2.5-MHz **Drift-Cancel Loop**

(Delay between cancellation paths is approximately  $1 \mu s$ )

dB. This causes most DA designs that use this technique (and this is attractive because of simplicity and cost) to have a relatively (to PLL) high noise floor, in the order of -130 to -135 dBC/Hz, in ultrahigh frequency (UHF). (Here dBC indicates decibels referred to *carrier*.) At a premium, the VCO can be replaced by a synthesizer. DA synthesizers will not be discussed in this text in great detail.

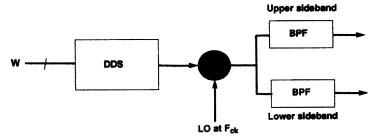

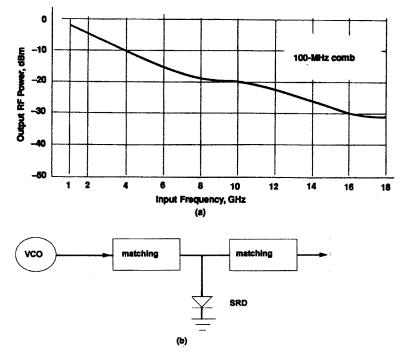

#### 1-4-3 Direct digital synthesis

DDS is an emerging and maturing signal generation technology. Up to 10 years ago, this technique was rather a novelty and was used in very limited applications. However, due to the enormous evolution of digital technologies (speed, integration, power, cost), digital signal processing (DSP), and data conversion devices, it is becoming increasingly popular, and its performance improves constantly.

There is a fundamental difference between DDS and DA or PLL. Although both PLL and DA techniques use digital devices, such as dividers and phase detectors, the PLL and DA techniques are fundamentally analog disciplines. The basic signal generator in both techniques is an oscillator, which is a feedback-tuned amplifier set to operate under specific conditions (controlled instability). The oscillator is manipulated to allow the generation of a range of frequencies. In DDS, the signal is generated and manipulated digitally from the "ground up," and after all the digital manipulations are completed, it is converted to an analog signal via a digital-to-analog converter (DAC).

The DDS is thus a computing machine where signals are repre-

sented by numbers and should be considered a DSP discipline. There are many compelling reasons to do this.

Signal generation is, after all, the heart of every electronic device and top of the list of standard industrial reasons to "go digital." Other engineering drivers such as producibility, repeatability, reliability, and very high accuracy demand the use of digital techniques, which now infiltrate not only DSP but also signal generation. DDS adds dimensions not possible with analog designs. In a way there is some similarity between the evolution of DDS and that of digital recording and the use of the *compact disk* (*CD*). The signal has high fidelity, waveforms have been converted to numbers (an old Pythagorean dream come true), there is total control of the signal parameters at all times, and the density of digital circuitry allows a very high level of integration in small size economically.

Thus, after years of maturity, DDS is finding many applications and has been established as a fundamental and important signal generation discipline.

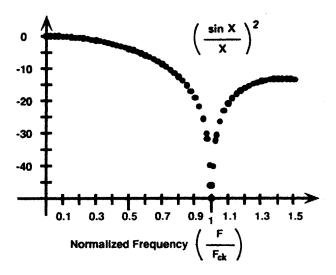

**1-4-3-1 Basic theory.** Like most DSP disciplines, the fundamental root of DDS is based on the sampling theorem, due to Shannon (see Chap. 4). The theorem states that any (stochastic, with finite energy) signal having a band-limited spectrum (i.e., the signal has no energy at frequencies above  $\omega_0 = W$ ), such a signal can be represented by its discrete samples in time, provided that the sampling rate is at least  $2F_0$ , where  $F_0 = \omega_0/2\pi$ . A simple proof is provided in Chap. 4.

The sampling theorem shows that such a signal can be fully recovered from its samples and that, in the process, many other frequencies are being generated. These "artifacts" are also referred to as the *aliasing signals*. (See App. 4A.) We will demonstrate an intuitive explanation of what is happening in the sampled data domain.

Suppose that a viewer sits in a dark room. In front of her there are a wheel and a single bar connecting the center of the wheel to the perimeter. Suppose also that a light source is set behind her and flashes very short flashes (almost like a delta function sampling) at the rate of 10 flashes per second.

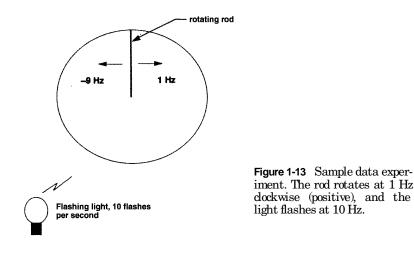

Now the wheel starts to rotate at 1 cycle per second, or 1 Hz, as seen in Fig. 1-13, say, clockwise. If the viewer is required to

describe what is happening in front of her eyes, she will not be able to give a conclusive answer. Note that what the viewer sees (which is the reality in this case) is the bar advancing 36° clockwise at every flash. Her interpretation will be that the wheel is rotating at 1 Hz, or 11 Hz, or 21 Hz, or at any frequency that is 10n + 1 Hz clockwise, but also at 9 Hz or 19 Hz or any frequency that is 10n - 1 Hz counterclockwise.

This is a cardinal point in DDS theory. The same results will be observed by the viewer if the bar is rotated at 10n + 1 or 10n - 1, or generally n (light sampling)  $\pm K$  (wheel frequency) rotations per second.

This interpretation of the experiment is, of course, the spectrum shown in the mathematical proof of the sampling theorem. The mathematical proof is enlightening by itself. We can interpret the clockwise rotations as positive frequencies and the counterclockwise rotations as negative frequencies. These negative frequencies are obviously as real as the positive ones and in DSP terminology are usually referred to as the *aliasing frequencies*.

A special interesting case arises when the rotation is exactly 5 Hz. At this point, all the positive and negative frequencies converge. This is referred to as the *Nyquist frequency* (half the sampling rate).

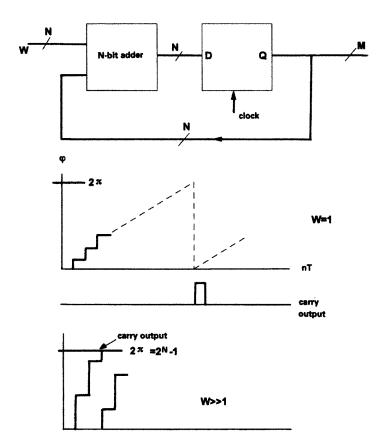

In DDS, the procedure of the signal sampling is reversed. And the process is therefore reversed. Suppose that, instead of sampling a sine wave, we generated its samples. (All can be calculated since the waveform is known; the sine is a perfectly known wave-

Figure 1-14 DDS block diagram and waveforms.

form, unlike a stochastic process that is random by nature.) Then according to the theorem it will be possible to reconstruct the sine wave signal perfectly.

In essence, that is what DDS is. The rest is details and techniques for efficient, economical, and fast executions.

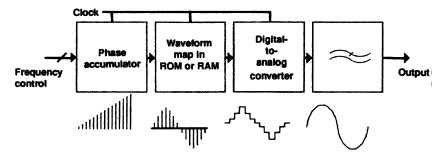

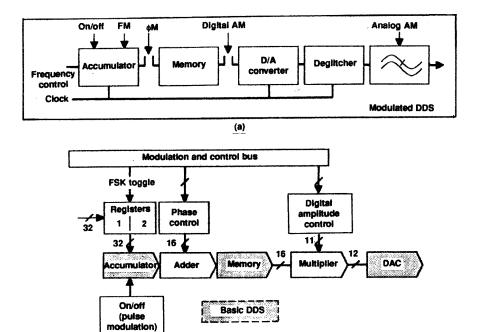

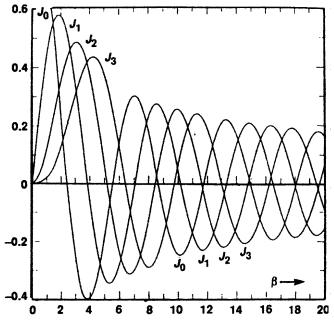

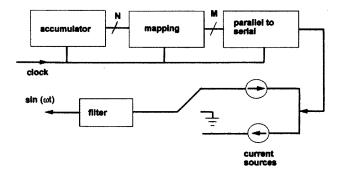

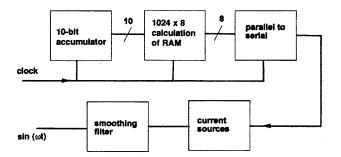

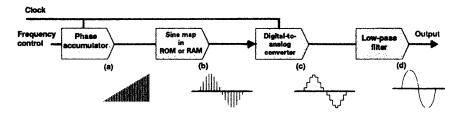

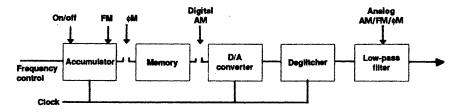

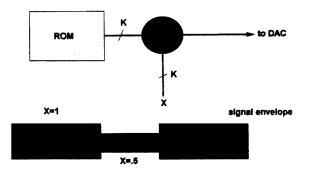

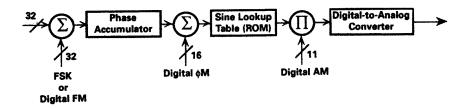

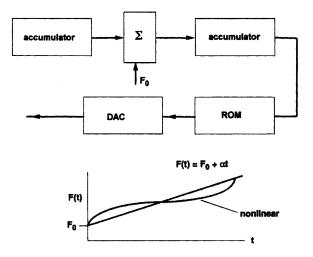

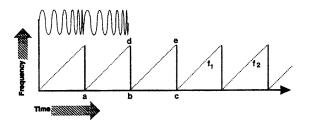

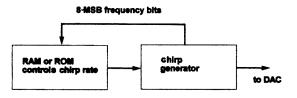

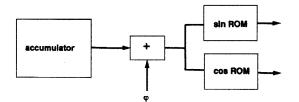

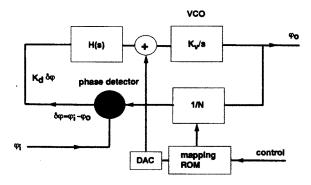

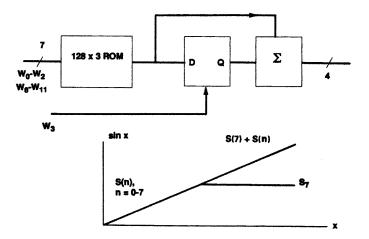

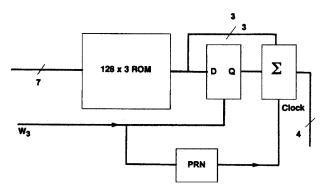

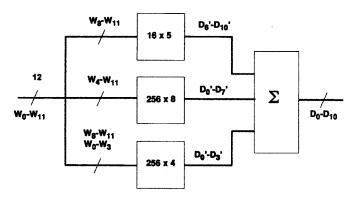

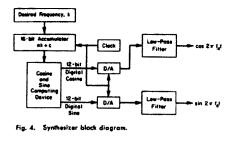

**1-4-3-2 DDS concepts.** There are a great variety of DDS implementations, as will be demonstrated in Chap. 4. However, the dominant one consists of four elements: an accumulator, a sine lookup table, a DAC, and a *low-pass filter* (*LPF*). See Fig. 1-14. Remembering that the presentation of a fixed-amplitude, fixed-frequency, and fixed-phase sine wave is given by

$$A\sin(\omega t + \varphi) \tag{1-40}$$

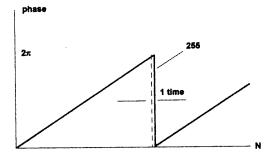

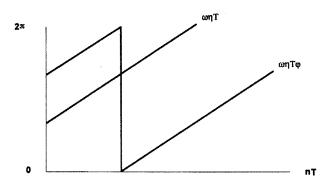

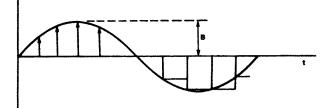

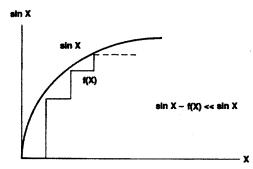

we can trace the signal buildup as follows: The signal phase is a linear function, as shown in Fig. 1-14. The gradient or slope of the phase  $d\varphi/dt$  is the angular frequency  $\omega$ . To generate the amplitude of the output waveform, it is necessary to transform the phase  $\varphi(t)$  to  $\sin[\varphi(t)]$ , and this is usually done by using a read-only memory (ROM), since the transformation is nonlinear and ROM (or RAM) is a convenient tool.

The output of the ROM is thus the digital representation of the sine wave signal amplitude, (digital) samples, and the DAC converts it to an analog sine wave. The LPF removes all the aliasing frequencies and causes the signal to appear smooth, as shown in Fig. 1-14. Note that since the signal is synthesized from the ground up, we know exactly the state of the machine at all times; and it is relatively easy to add phase shifting, frequency changes, and amplitude modulation, all in the digital domain and with digital accuracy.

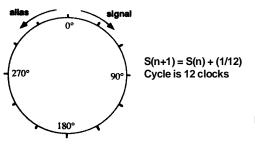

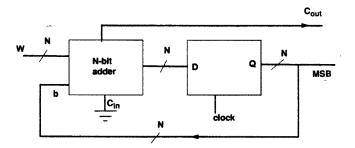

The accumulator is a device that performs the function

$$S(n) = S(n-1) + W$$

(1-41)

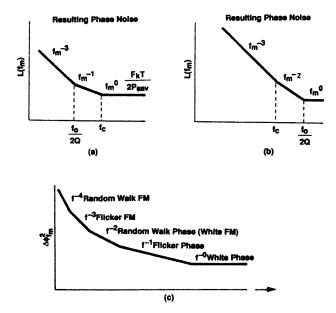

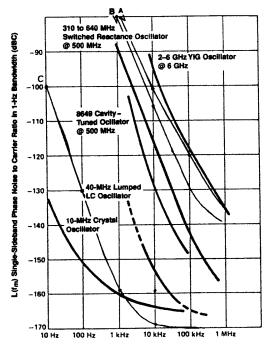

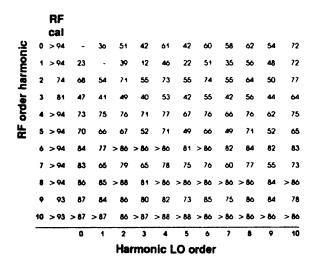

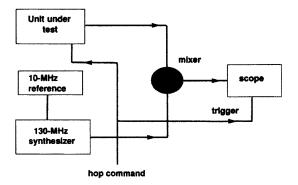

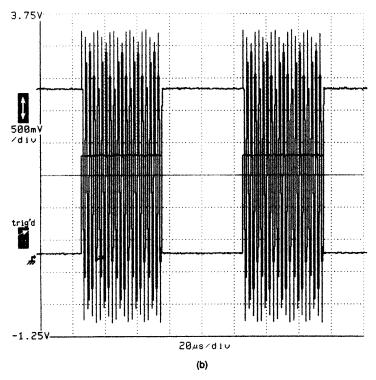

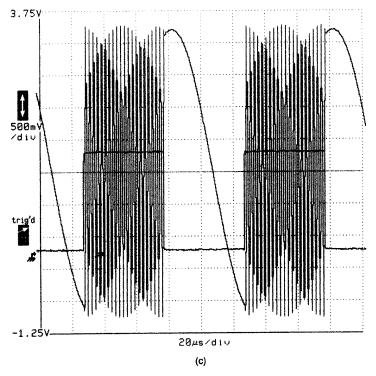

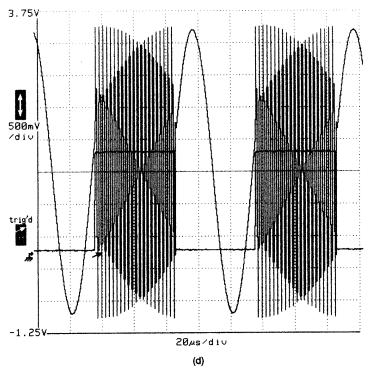

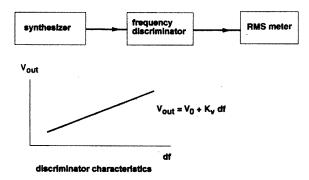

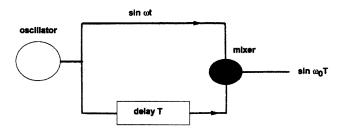

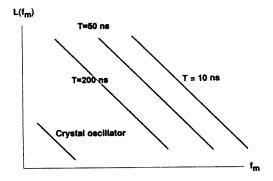

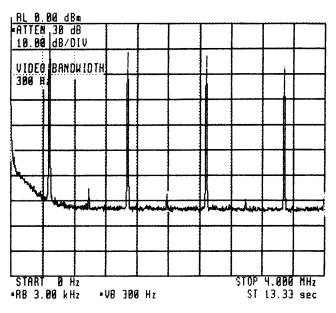

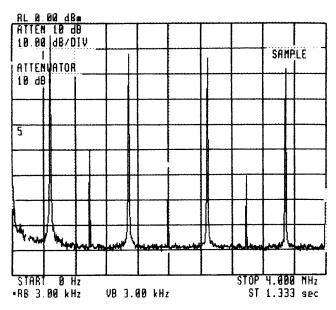

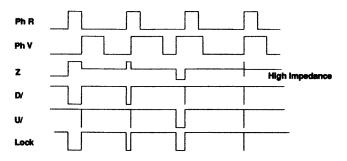

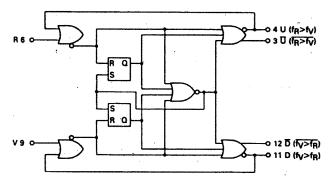

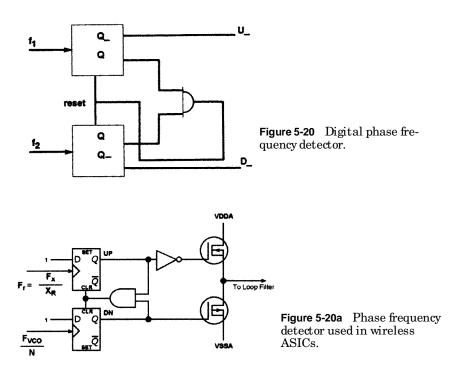

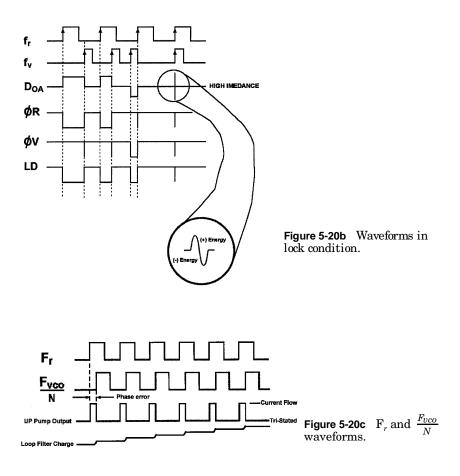

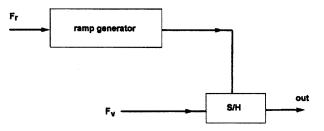

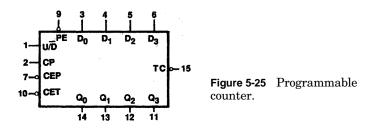

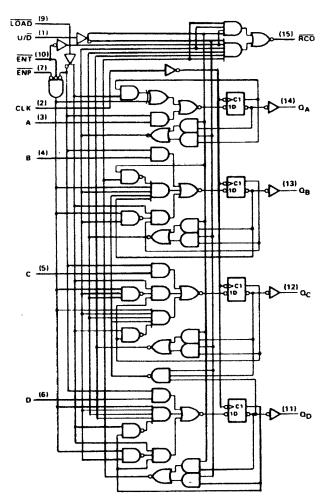

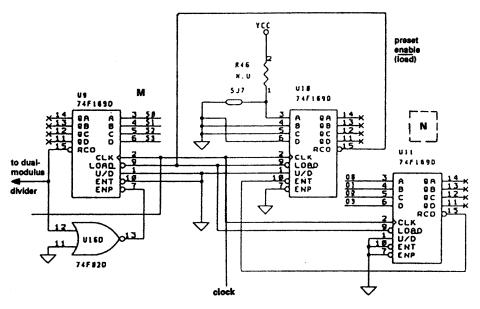

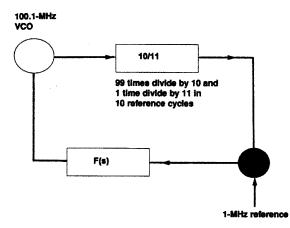

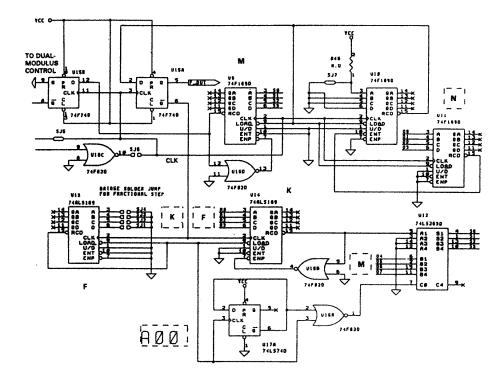

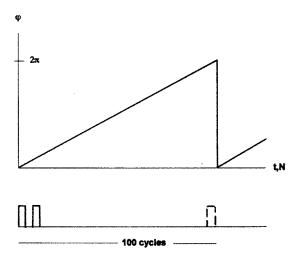

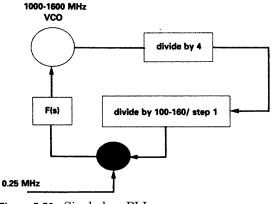

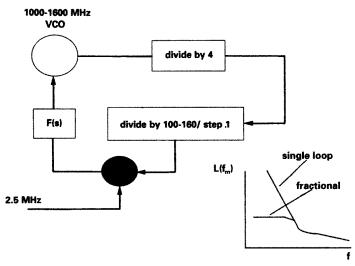

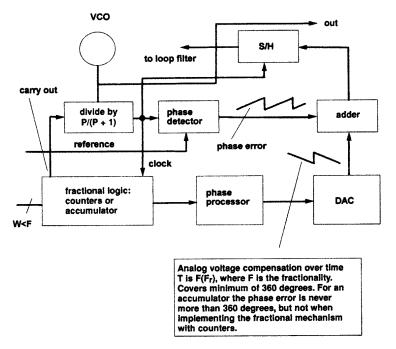

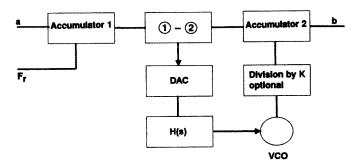

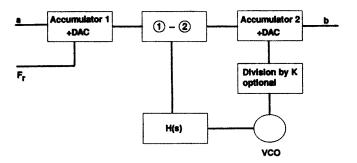

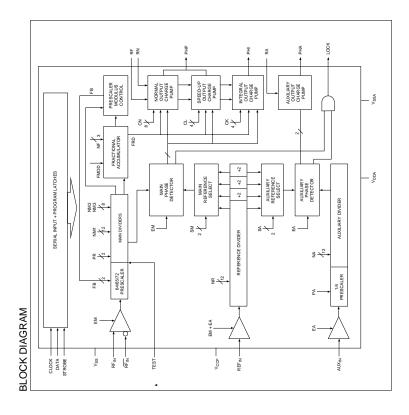

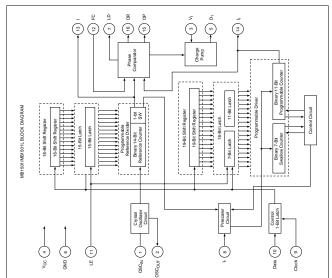

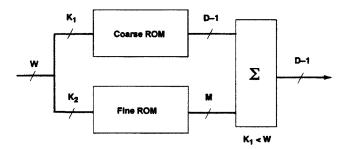

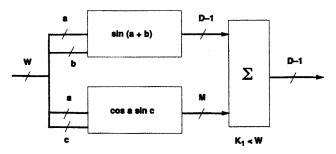

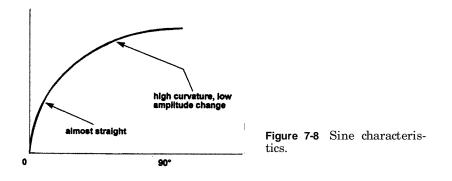

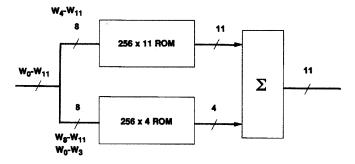

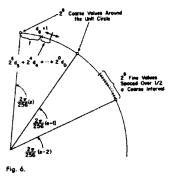

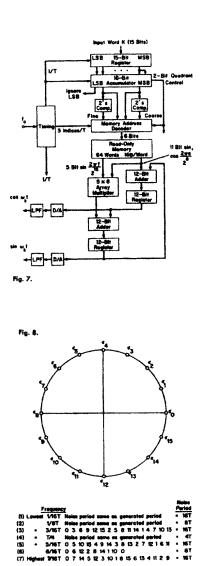

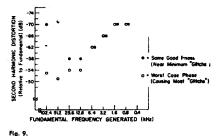

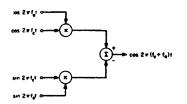

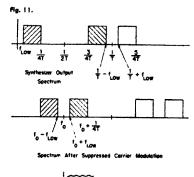

Such a device is a digital integrator and produces a linear output ramp whose slope (rate of change) is given by *W*, the input control word. This device is used to generate the phase  $\omega t$  or in the sample data  $W \cdot n \cdot T$ , where *T* is the sampling time and depends on the clock at which the accumulator runs. The accumulator is operating as an indexer whose output (representing the phase) controls the input to the ROM (or lookup) sine table, and can be viewed as a complex, yet easy to engineer and control, counter.